Инструмент проще, чем машина. Зачастую инструментом работают руками, а машину приводит в действие паровая сила или животное.

Компьютер тоже можно назвать машиной, только вместо паровой силы здесь электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

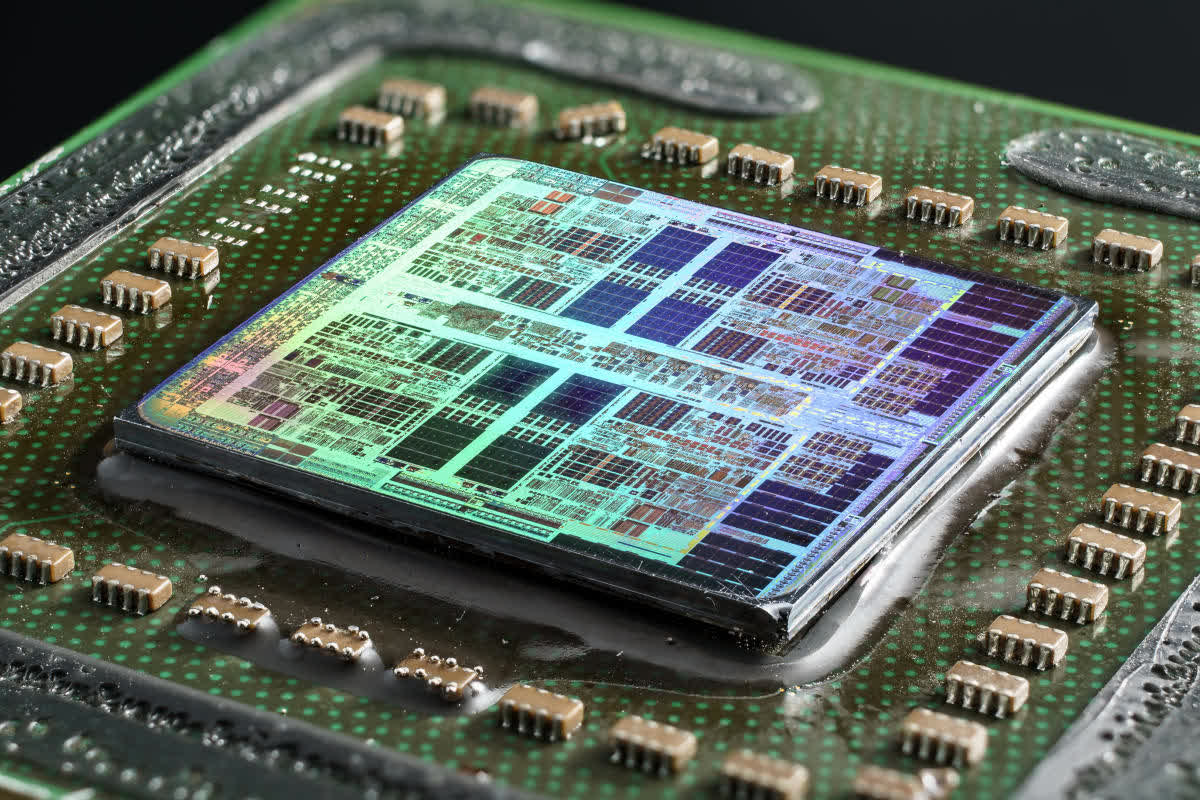

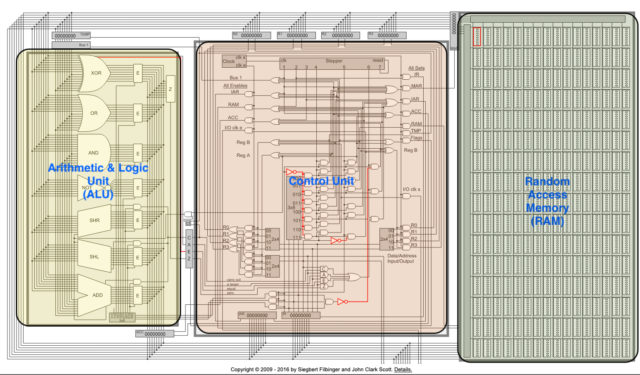

Процессор — это сердце/мозг любого компьютера. Его основное назначение — арифметические и логические операции, и прежде чем погрузиться в дебри процессора, нужно разобраться в его основных компонентах и принципах их работы.

Два основных компонента процессора

Устройство управления

Устройство управления (УУ) помогает процессору контролировать и выполнять инструкции. УУ сообщает компонентам, что именно нужно делать. В соответствии с инструкциями он координирует работу с другими частями компьютера, включая второй основной компонент — арифметико-логическое устройство (АЛУ). Все инструкции вначале поступают именно на устройство управления.

Существует два типа реализации УУ:

- УУ на жёсткой логике (англ. hardwired control units). Характер работы определяется внутренним электрическим строением — устройством печатной платы или кристалла. Соответственно, модификация такого УУ без физического вмешательства невозможна.

- УУ с микропрограммным управлением (англ. microprogrammable control units). Может быть запрограммирован для тех или иных целей. Программная часть сохраняется в памяти УУ.

УУ на жёсткой логике быстрее, но УУ с микропрограммным управлением обладает более гибкой функциональностью.

Арифметико-логическое устройство

Это устройство, как ни странно, выполняет все арифметические и логические операции, например сложение, вычитание, логическое ИЛИ и т. п. АЛУ состоит из логических элементов, которые и выполняют эти операции.

Большинство логических элементов имеют два входа и один выход.

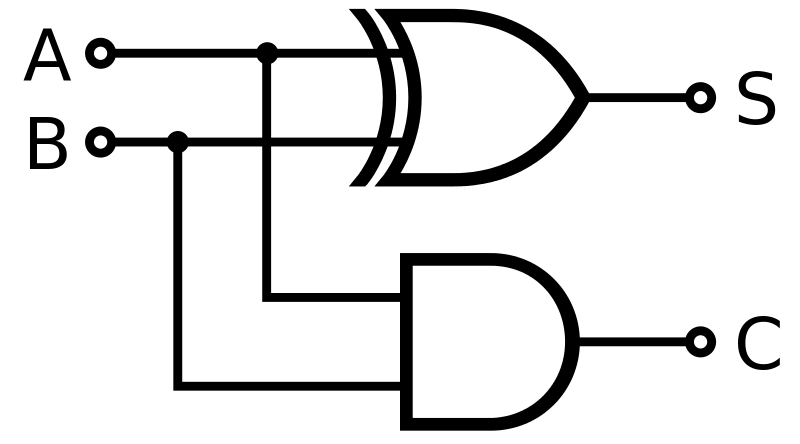

Ниже приведена схема полусумматора, у которой два входа и два выхода. A и B здесь являются входами, S — выходом, C — переносом (в старший разряд).

Схема арифметического полусумматора

Хранение информации — регистры и память

Как говорилось ранее, процессор выполняет поступающие на него команды. Команды в большинстве случаев работают с данными, которые могут быть промежуточными, входными или выходными. Все эти данные вместе с инструкциями сохраняются в регистрах и памяти.

Регистры

Регистр — минимальная ячейка памяти данных. Регистры состоят из триггеров (англ. latches/flip-flops). Триггеры, в свою очередь, состоят из логических элементов и могут хранить в себе 1 бит информации.

Прим. перев. Триггеры могут быть синхронные и асинхронные. Асинхронные могут менять своё состояние в любой момент, а синхронные только во время положительного/отрицательного перепада на входе синхронизации.

По функциональному назначению триггеры делятся на несколько групп:

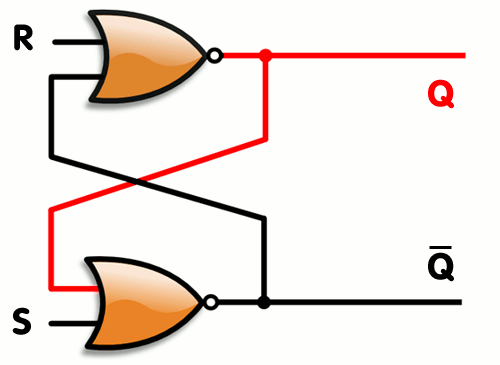

- RS-триггер: сохраняет своё состояние при нулевых уровнях на обоих входах и изменяет его при установке единице на одном из входов (Reset/Set — Сброс/Установка).

- JK-триггер: идентичен RS-триггеру за исключением того, что при подаче единиц сразу на два входа триггер меняет своё состояние на противоположное (счётный режим).

- T-триггер: меняет своё состояние на противоположное при каждом такте на его единственном входе.

- D-триггер: запоминает состояние на входе в момент синхронизации. Асинхронные D-триггеры смысла не имеют.

Для хранения промежуточных данных ОЗУ не подходит, т. к. это замедлит работу процессора. Промежуточные данные отсылаются в регистры по шине. В них могут храниться команды, выходные данные и даже адреса ячеек памяти.

Принцип действия RS-триггера

Память (ОЗУ)

ОЗУ (оперативное запоминающее устройство, англ. RAM) — это большая группа этих самых регистров, соединённых вместе. Память у такого хранилища непостоянная и данные оттуда пропадают при отключении питания. ОЗУ принимает адрес ячейки памяти, в которую нужно поместить данные, сами данные и флаг записи/чтения, который приводит в действие триггеры.

Прим. перев. Оперативная память бывает статической и динамической — SRAM и DRAM соответственно. В статической памяти ячейками являются триггеры, а в динамической — конденсаторы. SRAM быстрее, а DRAM дешевле.

Команды (инструкции)

Команды — это фактические действия, которые компьютер должен выполнять. Они бывают нескольких типов:

- Арифметические: сложение, вычитание, умножение и т. д.

- Логические: И (логическое умножение/конъюнкция), ИЛИ (логическое суммирование/дизъюнкция), отрицание и т. д.

- Информационные:

move,input,outptut,loadиstore. - Команды перехода:

goto,if ... goto,callиreturn. - Команда останова:

halt.

Прим. перев. На самом деле все арифметические операции в АЛУ могут быть созданы на основе всего двух: сложение и сдвиг. Однако чем больше базовых операций поддерживает АЛУ, тем оно быстрее.

Инструкции предоставляются компьютеру на языке ассемблера или генерируются компилятором высокоуровневых языков.

В процессоре инструкции реализуются на аппаратном уровне. За один такт одноядерный процессор может выполнить одну элементарную (базовую) инструкцию.

Группу инструкций принято называть набором команд (англ. instruction set).

Тактирование процессора

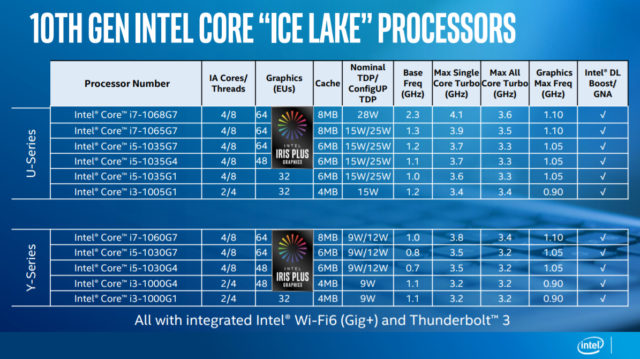

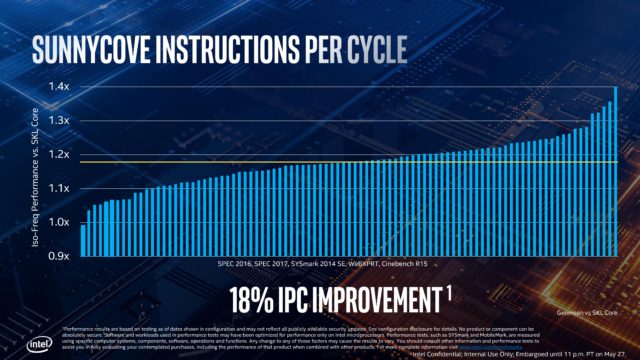

Быстродействие компьютера определяется тактовой частотой его процессора. Тактовая частота — количество тактов (соответственно и исполняемых команд) за секунду.

Частота нынешних процессоров измеряется в ГГц (Гигагерцы). 1 ГГц = 10⁹ Гц — миллиард операций в секунду.

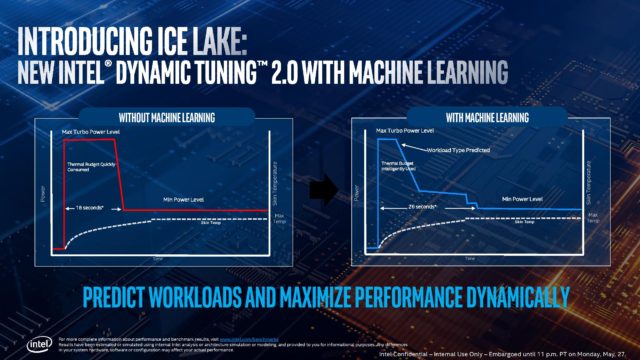

Чтобы уменьшить время выполнения программы, нужно либо оптимизировать (уменьшить) её, либо увеличить тактовую частоту. У части процессоров есть возможность увеличить частоту (разогнать процессор), однако такие действия физически влияют на процессор и нередко вызывают перегрев и выход из строя.

Выполнение инструкций

Инструкции хранятся в ОЗУ в последовательном порядке. Для гипотетического процессора инструкция состоит из кода операции и адреса памяти/регистра. Внутри управляющего устройства есть два регистра инструкций, в которые загружается код команды и адрес текущей исполняемой команды. Ещё в процессоре есть дополнительные регистры, которые хранят в себе последние 4 бита выполненных инструкций.

Ниже рассмотрен пример набора команд, который суммирует два числа:

LOAD_A 8. Это команда сохраняет в ОЗУ данные, скажем,<1100 1000>. Первые 4 бита — код операции. Именно он определяет инструкцию. Эти данные помещаются в регистры инструкций УУ. Команда декодируется в инструкциюload_A— поместить данные1000(последние 4 бита команды) в регистрA.LOAD_B 2. Ситуация, аналогичная прошлой. Здесь помещается число 2 (0010) в регистрB.ADD B A. Команда суммирует два числа (точнее прибавляет значение регистраBв регистрA). УУ сообщает АЛУ, что нужно выполнить операцию суммирования и поместить результат обратно в регистрA.STORE_A 23. Сохраняем значение регистраAв ячейку памяти с адресом23.

Вот такие операции нужны, чтобы сложить два числа.

Шина

Все данные между процессором, регистрами, памятью и I/O-устройствами (устройствами ввода-вывода) передаются по шинам. Чтобы загрузить в память только что обработанные данные, процессор помещает адрес в шину адреса и данные в шину данных. Потом нужно дать разрешение на запись на шине управления.

Кэш

У процессора есть механизм сохранения инструкций в кэш. Как мы выяснили ранее, за секунду процессор может выполнить миллиарды инструкций. Поэтому если бы каждая инструкция хранилась в ОЗУ, то её изъятие оттуда занимало бы больше времени, чем её обработка. Поэтому для ускорения работы процессор хранит часть инструкций и данных в кэше.

Если данные в кэше и памяти не совпадают, то они помечаются грязными битами (англ. dirty bit).

Поток инструкций

Современные процессоры могут параллельно обрабатывать несколько команд. Пока одна инструкция находится в стадии декодирования, процессор может успеть получить другую инструкцию.

Однако такое решение подходит только для тех инструкций, которые не зависят друг от друга.

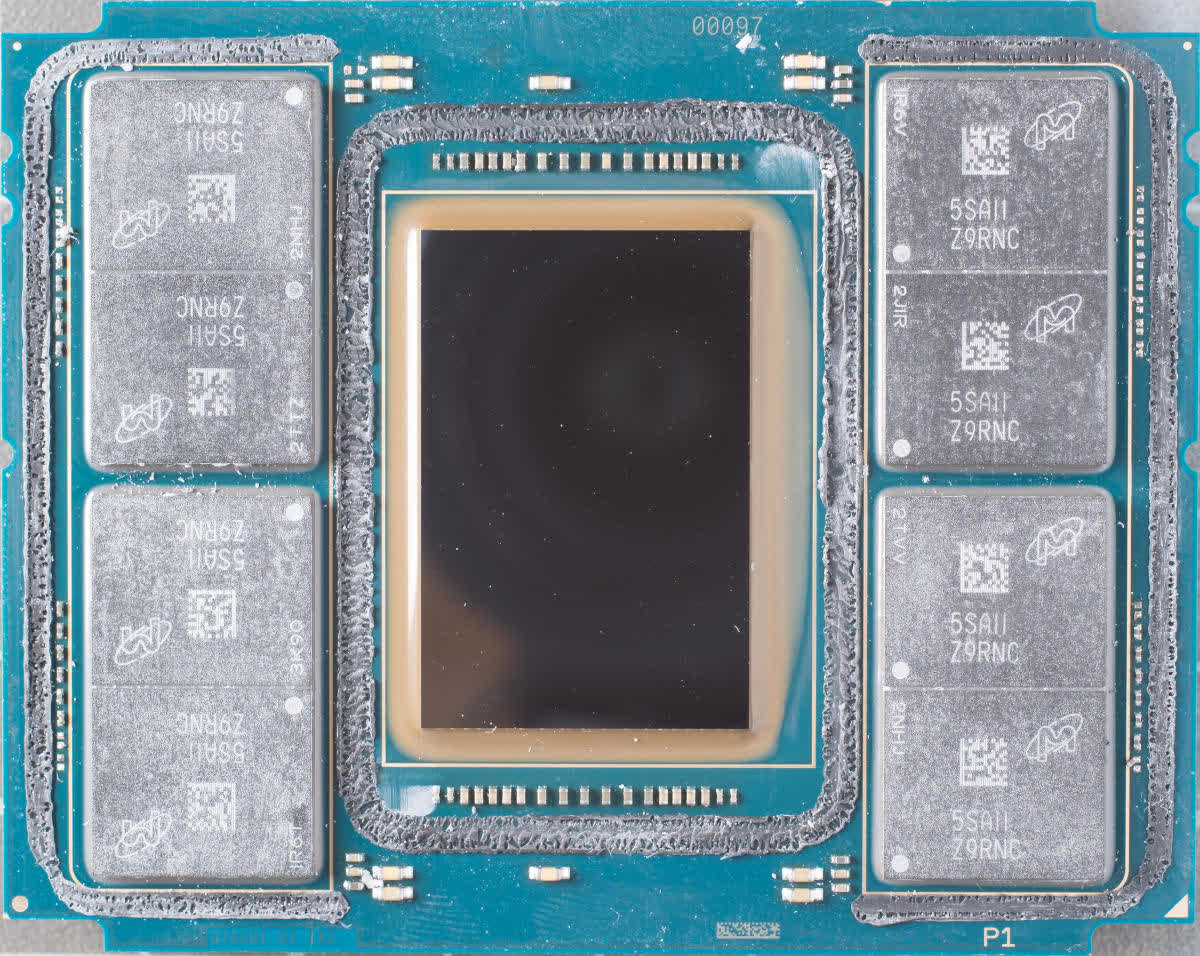

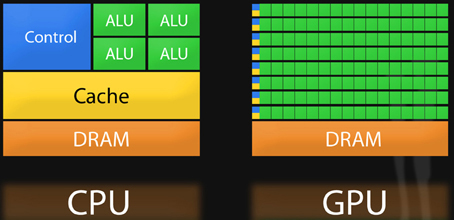

Если процессор многоядерный, это означает, что фактически в нём находятся несколько отдельных процессоров с некоторыми общими ресурсами, например кэшем.

Если хотите узнать о процессорах больше, посмотрите, какие бывают популярные архитектуры: CISC, RISC, MISC и другие и виды.

180К открытий197К показов

Путешествие через вычислительный конвейер процессора

Время на прочтение16 мин

Количество просмотров137K

Так как карьера программиста тесно связана с процессором, неплохо бы знать как он работает.

Что происходит внутри процессора? Сколько времени уходит на исполнение одной инструкции? Что значит, когда новый процессор имеет 12, или 18, или даже 31-уровневый конвейер?

Программы обычно работают с процессором, как с чёрным ящиком. Инструкции входят и выходят из него по порядку, а внутри совершается некая вычислительная магия.

Программисту полезно знать, что происходит внутри этого ящика, особенно, если он будет заниматься оптимизацией программ. Если вы не знаете какие процессы протекают внутри процессора, как вы сможете оптимизировать под него?

Эта статья рассказывает, как устроен вычислительный конвейер x86 процессора.

Вещи, которые вы уже должны знать

Во-первых, предполагается, что вы немного разбираетесь в программировании или может даже немного знаете ассемблер. Если вы не понимаете, что я имею ввиду, когда использую термин «указатель на инструкцию» (instruction pointer), тогда, возможно, эта статья не для вас. Когда я пишу о регистрах, инструкциях и кэшах, я предполагаю, что вы уже знаете, что это значит, можете понять или нагуглить.

Во-вторых, эта статья – упрощение сложной темы. Если вам кажется, что я пропустил какие-то важные моменты, добро пожаловать в комментарии.

В-третьих, я акцентирую внимание только на процессорах Intel x86 семейства. Я знаю о существовании других семейств процессоров, кроме x86. Я знаю, что AMD внесло много полезных нововведений в x86 семейство, и Intel их приняло. Но архитектура и набор инструкций принадлежит Intel, также Intel представило реализацию самых главных особенностей семейства, так что для простоты и логичности, речь пойдет именно об их процессорах.

В-четвертых, эта статья уже устарела. В разработке более новые процессоры, и некоторые из них уже скоро ожидаются в продаже. Я очень рад, что технологии развиваются такими быстрыми темпами и надеюсь, что когда-нибудь все стадии, описанные ниже, полностью устареют и будут заменены еще более удивительными достижениями в процессоростроении.

Основы вычислительного конвейера

Если посмотреть на x86 семейство в целом, то можно заметить, что оно не сильно изменилось за 35 лет. Было много дополнений, но оригинальный дизайн, как и почти весь набор команд, в основном остались нетронутыми и до сих пор прослеживаются в современных процессорах.

Первоначальный 8086 процессор имеет 14 регистров, которые используются до сих пор. Четыре регистра общего назначения – AX, BX, CX и DX. Четыре сегментных регистра, которые используют для облегчения работы с указателями – CS (Code Segment), DS (Data Segment), ES (Extra Segment) и SS (Stack Segment). Четыре индексных регистра, которые указывают на различные адреса в памяти – SI (Source Index), DI (Destination Index), BP (Base Pointer) и SP (Stack Pointer). Один регистр содержит битовые флаги. И, наконец, самый главный регистр в этой статье – IP (Instruction Pointer).

IP регистр – это указатель с особой функцией, его задача указывать на следующую инструкцию, которая подлежит исполнению.

Все процессоры в x86 семействе следуют одному и тому же принципу. Сначала они следуют указателю на инструкцию и декодируют следующую команду по этому адресу. После декодирования следует этап выполнения этой инструкции. Некоторые инструкции читают из памяти или пишут в нее, другие производят вычисления, сравнения или другую работу. Когда работа окончена, команда проходит через этап отставки (retire stage) и IP начинает указывать на следующую инструкцию.

Этот принцип декодирования, выполнения и отставки одинаково применяется как в первом 8086 процессоре, так и в самом последнем Core i7. С течением времени были добавлены новые этапы конвейера, но принцип работы остался прежним.

Что изменилось за 35 лет

Первые процессоры были просты по сегодняшним меркам. 8086 процессор начинал с проверки команды на текущем указателе на инструкцию, декодировал ее, выполнял, отставлял и продолжал работу со следующей инструкцией на которую указывал IP.

Каждый новый чип в семействе добавлял новую функциональность. Большинство добавляло новые инструкции, некоторые добавляли новые регистры. Чтобы оставаться в рамках этой статьи, я буду уделять внимание изменениям, которые непосредственно касаются прохождения команд через ЦП. Другие изменения, такие как добавление виртуальной памяти или параллельной обработки, конечно же интересны, но выходят за рамки данной статьи.

В 1982 был введён кэш инструкций. Вместо обращения к памяти на каждой команде, процессор читал на несколько байт дальше текущего IP. Кэш инструкций был всего несколько байт в размере, достаточным для хранения лишь нескольких команд, но ощутимо увеличивал производительность, исключая постоянные обращения к памяти каждые несколько тактов.

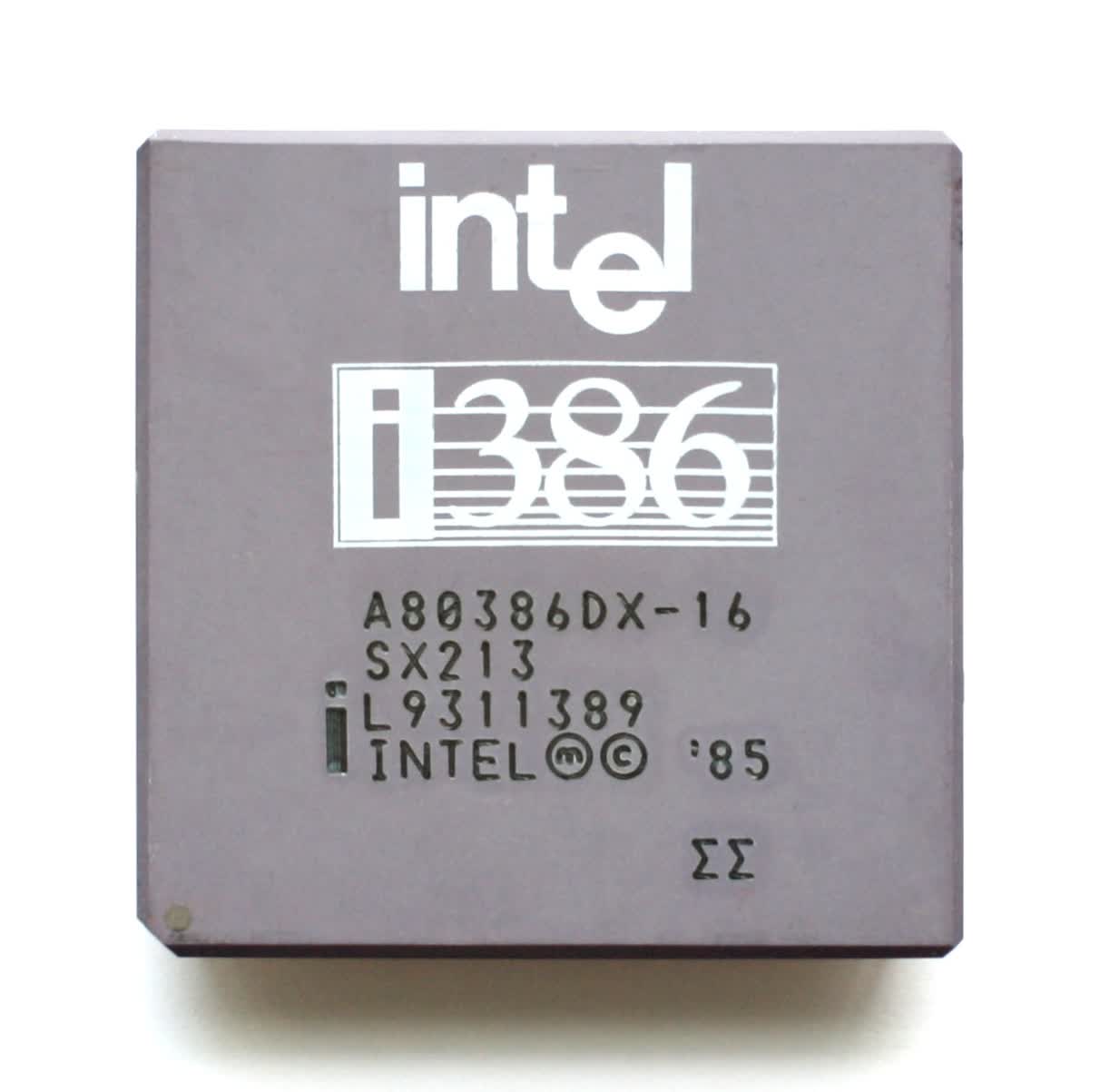

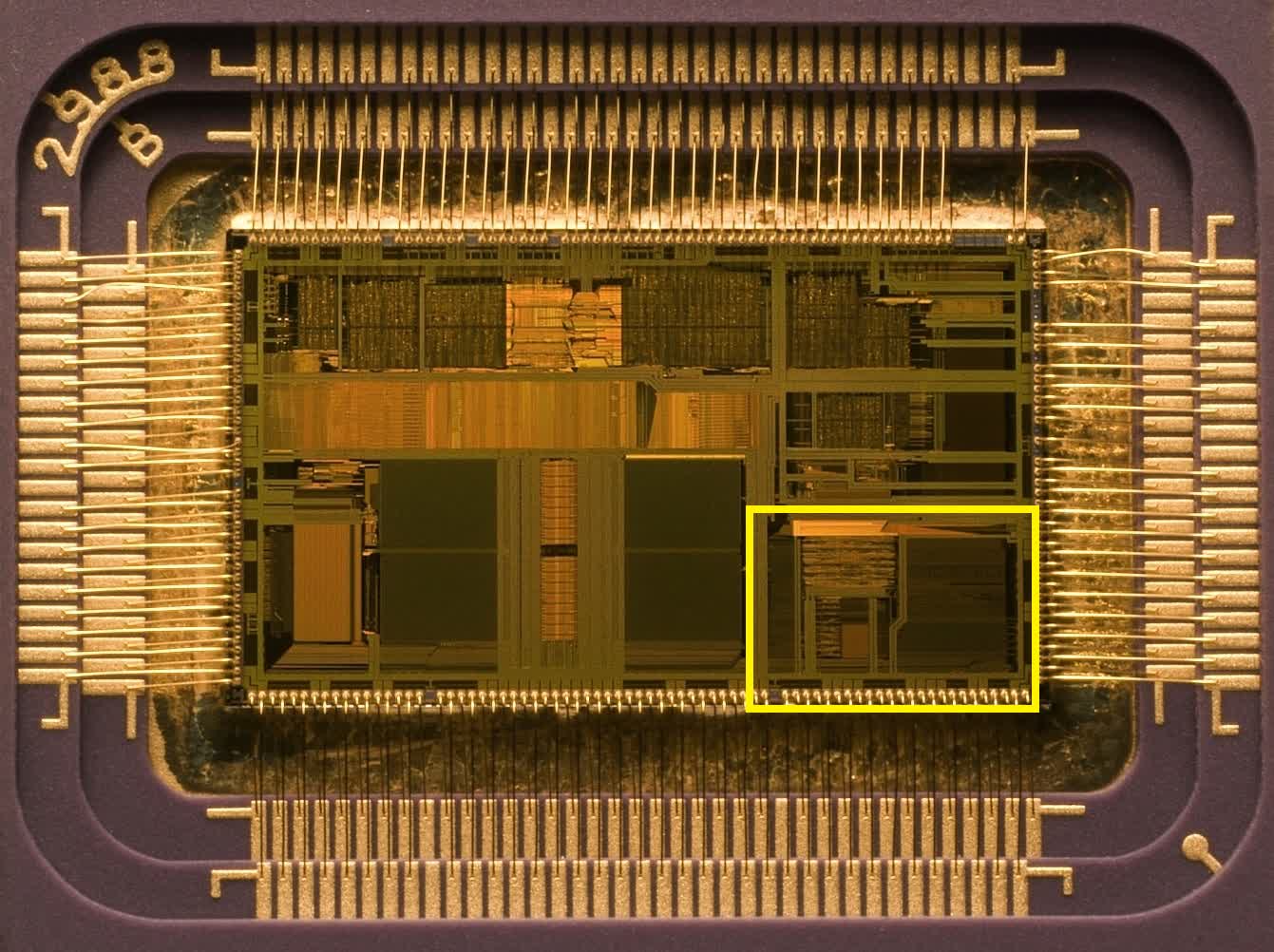

В 1985 в 386 процессор был добавлен кэш данных и увеличен размер кэша инструкций. Этот шаг позволил увеличить производительность за счет чтения на несколько байт дальше запроса на данные. На тот момент кэши данных и инструкций измерялись в килобайтах, нежели в байтах.

В 1989 i486 процессор перешел на 5-уровневый конвейер. Вместо наличия одной инструкции во всем процессоре, теперь каждый уровень конвейера мог иметь по инструкции. Это нововведение позволило увеличить производительность более чем в два раза по сравнению с 386 процессором на той частоте. Этап загрузки (fetch stage) извлекал команду из кэша инструкций (размер кэша в то время был обычно 8кб). Второй этап декодировал инструкцию. Третий этап транслировал адреса памяти и смещения, необходимые для команды. Четвёртый этап выполнял инструкцию. Пятый этап отправлял команду в отставку и записывал результаты обратно в регистры и память по мере необходимости. Появление возможности держать в процессоре множество инструкций одновременно позволило программам выполняться гораздо быстрее.

1993 год был годом появления процессора Pentium. Название семейства процессоров сменилось с номеров на имена из-за судебного процесса, поэтому оно было названо Pentium вместо 586. Конвейер чипа изменился еще больше по сравнению с i486. Архитектура Pentium добавила второй отдельный суперскалярный конвейер. Основной конвейер работал также, как и на i486, в то время как второй выполнял более простые инструкции, такие как целочисленная арифметика, параллельно и намного быстрее.

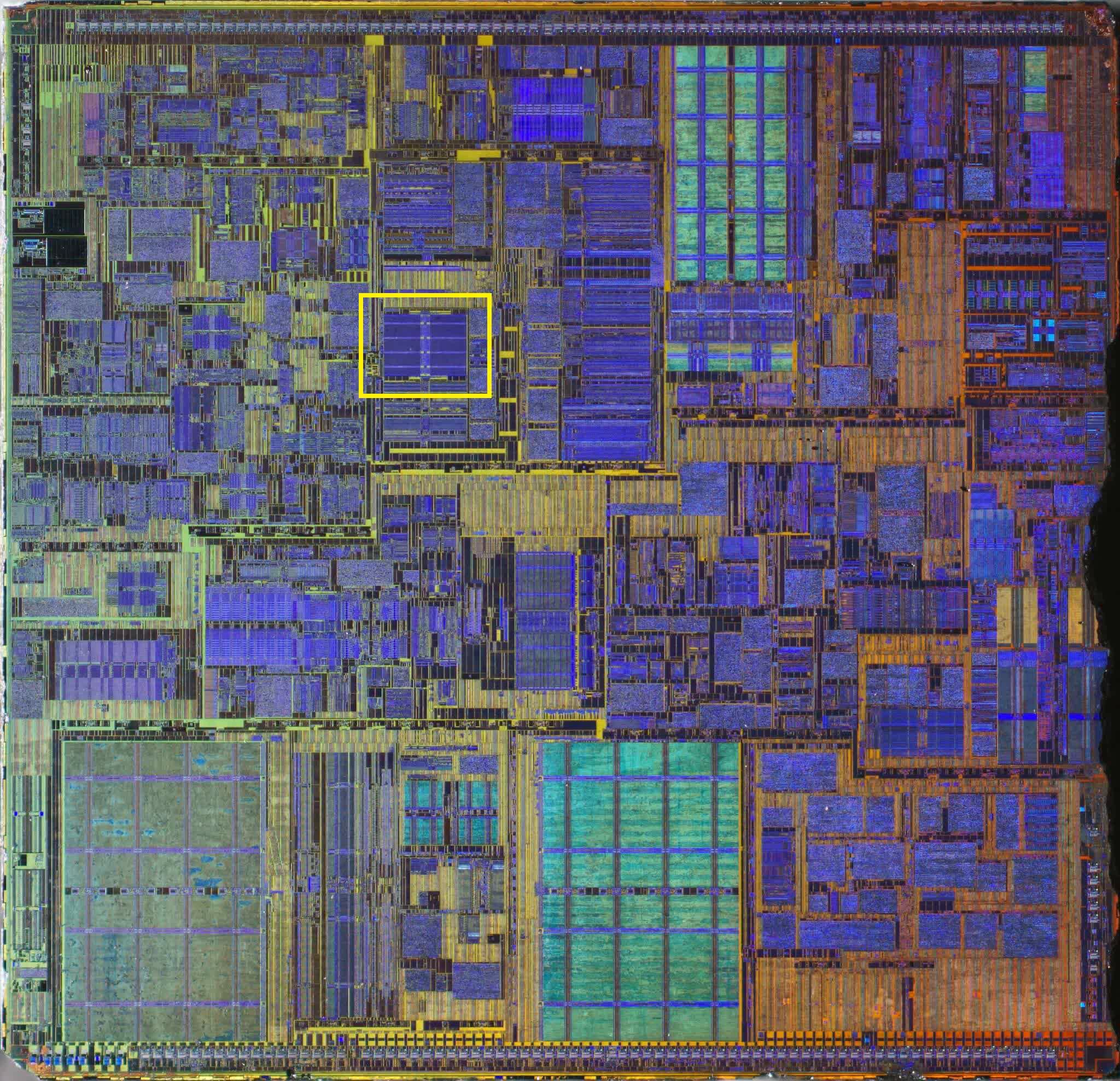

В 1995 Intel выпустило процессор Pentium Pro, который имел кардинальные изменения в дизайне. У чипа появилось несколько особенностей, включая ядро с внеочерёдным (Out-of-Order, OOO) и упреждающим (Speculative) исполнением команд. Конвейер был расширен до 12 этапов, и в него вошло нечто, называемое суперконвейером (superpipeline), где большое количество инструкций могло исполняться одновременно. OOO ядро будет более подробно освещено ниже в статье.

Между 1995 годом, когда OOO ядро было представлено, и 2002 было сделано много важных изменений. Были добавлены дополнительные регистры и представлены инструкции, которые могли обрабатывать множество данных за раз (Single Instruction Multiple Data, SIMD). Появились новые кэши, старые увеличились в размере. Этапы конвейера делились и объединялись, адаптируясь к требованиям реального мира. Эти и многие другие изменения были важны для общей производительности, но мало что значили, когда речь шла о потоке данных через процессор.

В 2002 Pentium 4 представил новую технологию — Hyper-Threading. OOO ядро было настолько успешным в обработке команд, что способно было обрабатывать инструкции быстрее, чем они могли быть посланы ядру. Для большинства пользователей OOO ядро процессора практически бездействовало большую часть времени даже под нагрузкой. Для обеспечения постоянного потока инструкций к OOO ядру добавили второй фронт-энд. Операционная система видела два процессора вместо одного. Процессор содержал два набора x86 регистров, два декодера инструкций, которые следили за двумя наборами IP и обрабатывали два набора инструкций. Далее команды обрабатывались одним общим OOO ядром, но это было незаметно для программ. Потом инструкции проходили этап отставки, как и ранее, и посылались назад к виртуальным процессорам, на которые они поступали.

В 2006 Intel выпустило микроархитектуру Core. В маркетинговых целях она была названа Core 2 (потому что каждый знает, что два лучше, чем один). Неожиданным ходом было снижение частоты процессоров и отказ от Hyper-Threading. Снижение частот способствовало расширению всех этапов вычислительного конвейера. OOO ядро было расширено, кэши и буферы были увеличены. Архитектура процессоров была переработана с уклоном на двух- и четырёхъядерные чипы с общими кэшами.

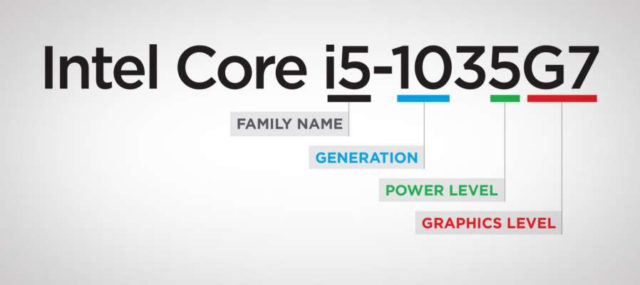

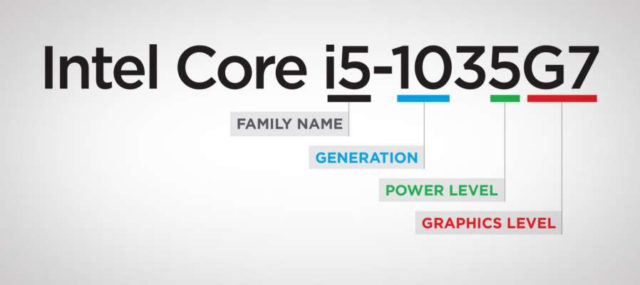

В 2008 Intel ввело схему именования процессоров Core i3, Core i5 и Core i7. В этих процессорах вновь появился Hyper-Threading с общим OOO ядром, и отличались они, в основном, лишь размерами кэшей.

Будущие процессоры: Следующее обновление микроархитектуры, названной Haswell, по слухам, будет выпущено во второй половине 2013. Опубликованные на данный момент документы говорят о том, что это будет 14-уровневый конвейер, и, скорей всего, принцип обработки информации будет все также следовать дизайну Pentium Pro.

Так что же такое этот вычислительный конвейер, что такое OOO ядро и как это все увеличивает скорость обработки?

Вычислительный конвейер процессора

В самом простой форме, описанной выше, одиночная инструкция входит в процессор, обрабатывается и выходит с другой стороны. Это довольно интуитивно для большинства программистов.

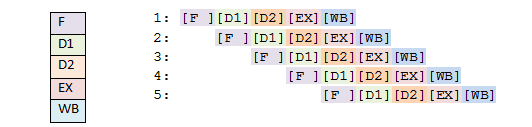

Процессор i486 имел 5-уровневый конвейер – загрузка (Fetch), основное декодирование (D1), вторичное декодирование или трансляция (D2), выполнение (EX), запись результата в регистры и память (WB). Каждый этап конвейера мог содержать по инструкции.

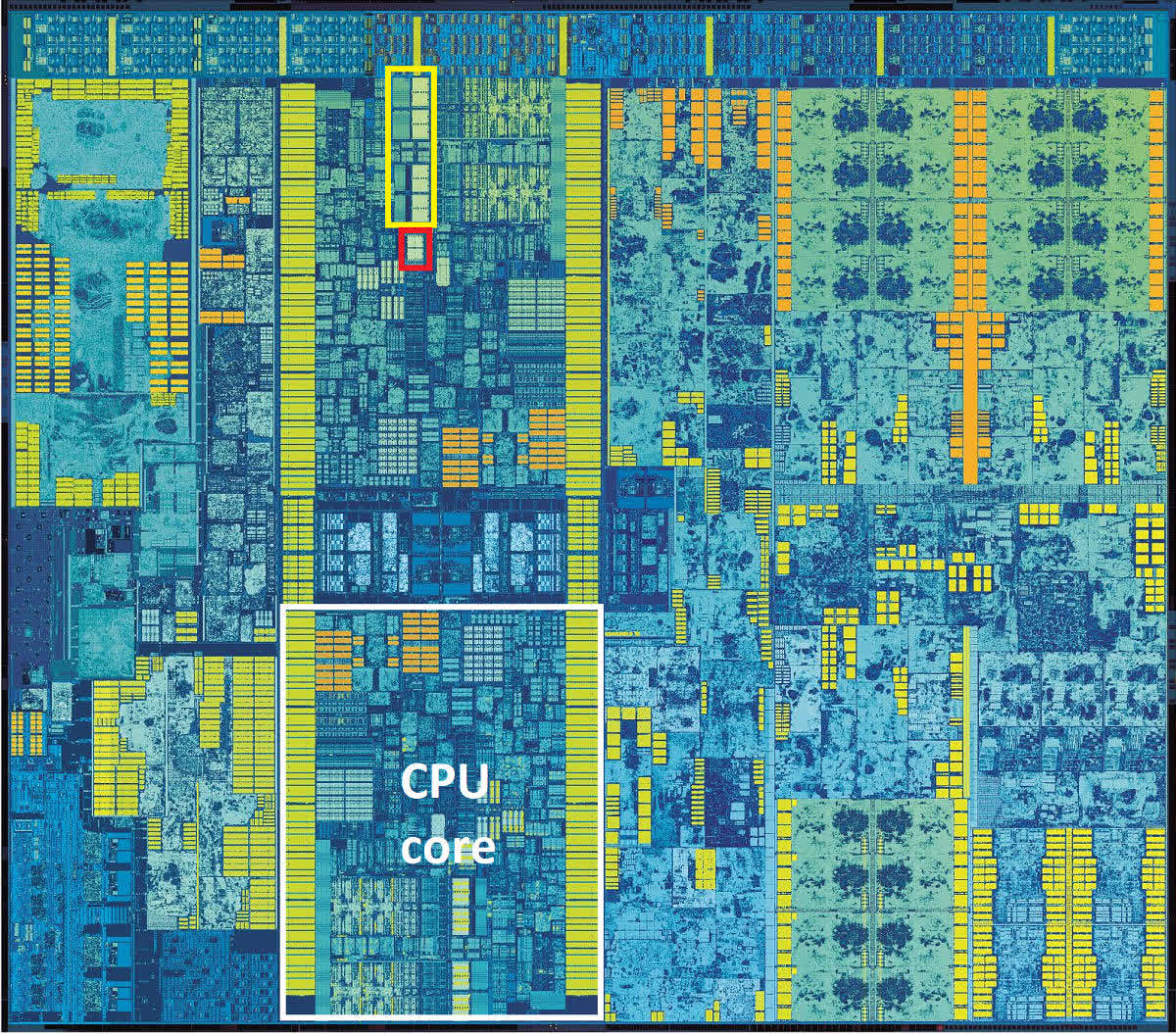

Конвейер i486 и пять инструкций, проходящие через него одновременно.

Однако такая схема имела серьезный недостаток. Представьте себе код ниже. До прихода конвейера следующие три строки кода были распространенным способом поменять значения двух переменных без использования третьей.

XOR a, b

XOR b, a

XOR a, b

Чипы, начиная с 8086 и до 386 не имели внутреннего конвейера. Они обрабатывали только одну инструкцию в каждый момент времени, независимо и полностью. Три последовательных XOR инструкции в такой архитектуре вовсе не проблема.

Теперь подумаем, что происходит с i486, так как это был первый x86 чип с конвейером. Наблюдать за многими вещами в движении одновременно может быть затруднительно, поэтому, возможно, вы сочтёте полезным обратиться к диаграмме выше.

Первая инструкция входит в этап загрузки, на этом первый шаг закончен. Следующий шаг – первая инструкция входит в D1 этап, вторая инструкция помещается в этап загрузки. Третий шаг – первая инструкция двигается в D2 этап, вторая в D1 и третья загружается в Fetch. На следующем шагу что-то идет не так – первая инструкция переходит в EX…, но остальные остаются на месте. Декодер останавливается, потому что вторая XOR команда требует результат первой. Переменная «a» должна быть использована во второй инструкции, но в неё не будет произведена запись, пока не выполнилась первая инструкция. Поэтому команды в конвейере ждут, пока первая команда не пройдет EX и WB этапы. Только после этого вторая инструкция может продолжить свой путь по конвейеру. Третья команда аналогично застрянет в ожидании выполнения второй команды.

Такое явление называется ступор конвейера (pipeline stall) или конвейерный пузырь (pipeline bubble).

Другой проблемой конвейеров является возможность одних инструкций выполняться очень быстро, а других очень медленно, что было более заметно с двойным конвейером Pentium.

Pentium Pro представил с собой 12-уровневый конвейер. Когда это число было впервые озвучено, то понимавшие как работал суперскалярный конвейер программисты затаили дыхание. Если бы Intel последовало такому же принципу с 12-уровневым конвейером, то любой ступор конвейера или медленная инструкция серьезно бы сказывались на производительности. Но в то же время Intel анонсировало кардинально отличающийся конвейер, названный ядром с внеочерёдным исполнением (OOO core). Несмотря на то, что это трудно было понять из документации, Intel заверило разработчиков, что они будут потрясены результатами.

Давайте разберем OOO ядро более детально.

OOO конвейер

В случае с OOO ядром, иллюстрация стоит тысячи слов. Так что давайте посмотрим несколько картинок.

Диаграмы конвейеров процессора

5-уровневый конвейер i486 работал замечательно. Эта идея была довольно распространена среди других семейств процессоров в то время и работала отлично в реальных условиях.

Суперскалярный конвейер i486.

Конвейер Pentium был даже еще лучше i486. Он имел два вычислительных конвейера, которые могли работать параллельно, и каждый из них мог содержать множество инструкций на различных этапах, позволяя вам обрабатывать почти в двое больше инструкций за то же время.

Два параллельных суперскалярных конвейера Pentium.

Однако наличие быстрых команд, ожидающих выполнение медленных, было все также проблемой в параллельных конвейерах, как и наличие последовательных команд (привет ступор). Конвейеры были все так же линейными и могли сталкиваться с непреодолимыми ограничениями производительности.

Дизайн OOO ядра сильно отличался от предыдущих чипов с линейными путями. Сложность конвейера возросла, и были введены нелинейные пути.

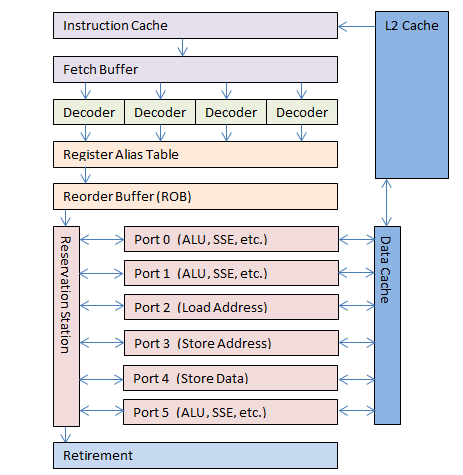

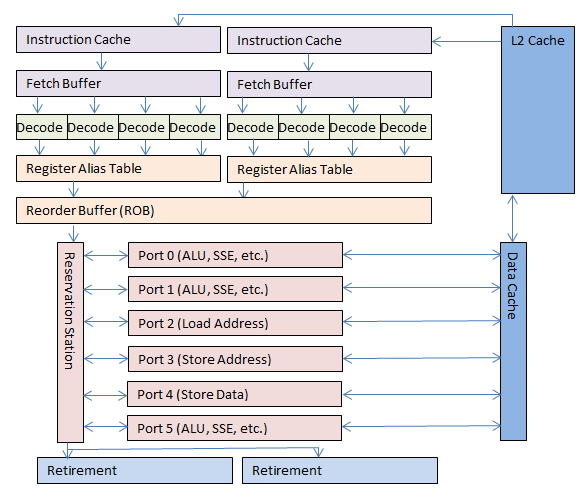

OOO ядро, используемое с 1995 года. Цветовое обозначение соответствует пяти этапам, используемых в предыдущих процессорах. Некоторые этапы и буферы не показаны, так как варьируются от процессора к процессору.

Сначала инструкции загружаются из памяти и помещаются в кэш инструкций процессора. Декодер современного процессора может предсказать появление скорого ветвления (например вызов функции) и начать загрузку инструкций заранее.

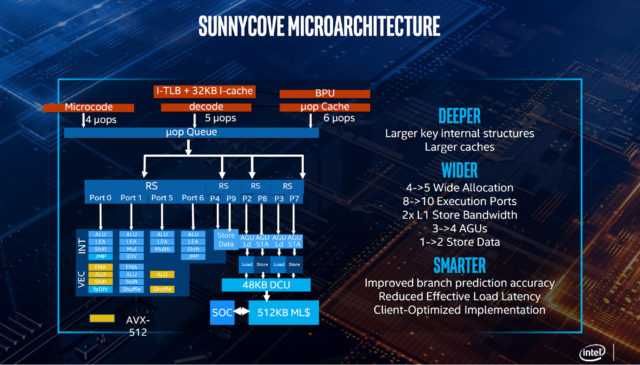

Этап декодирования был немного изменен по сравнению с более ранними чипами. Вместо обработки лишь одной инструкции на IP, Pentium Pro мог декодировать до трех инструкций за такт. Сегодняшние процессоры (2008-2013) могут декодировать до четырёх инструкций за такт. Результатом декодирования являются микрооперации (micro-ops / µ-ops).

Следующий этап (или группа этапов) состоит из трансляции микроопераций (micro-op transaltion) и последующего присвоения псевдонимов регистрам (register aliasing). Множество операций выполняются одновременно, возможно внеочерёдно, поэтому одна инструкция может читать из регистра, пока другая в него пишет. Запись в регистр может подавить значение, нужное другой инструкции. Оригинальные регистры внутри процессора (AX, BX, CX, DX итд.) транслируются (или создаются псевдонимы) во внутренние, скрытые от программиста регистры. Значение регистров и адресов памяти затем должны быть привязаны к временным значениям для обработки. На данный момент 4 микрооперации могут проходить через этап трансляции за такт.

После трансляции все микрооперации входят в буфер переупорядочивания (reorder buffer, ROB). На данный момент этот буфер может вмещать до 128 микроопераций. На процессорах с HT ROB также может выступать в роли координатора входных команд с виртуальных процессоров, распределяя два потока команд на одно OOO ядро.

Теперь микрооперации готовы для обработки и помещаются в резервацию (reservation station, RS). RS на данный момент может вмещать 36 микроопераций в любой момент времени.

Теперь настало время для магии OOO ядра. Микрооперации обрабатываются одновременно на множестве исполнительных блоков (execution unit), причем каждый блок работает максимально быстро. Микрооперации могут обрабатываться внеочерёдно, если все нужные данные для этого уже доступны. Если данные недоступны, выполнение откладывается до их готовности, пока выполняются другие готовые микрооперации. Таким образом долгие операции не блокируют быстрые и последствия ступора конвейера уже не так печальны.

OOO ядро Pentium Pro имело шесть исполнительных блоков: два для работы с целыми числами, один для чисел с плавающей точкой, загрузочный блок, блок сохранения адресов и блок сохранения данных. Два целочисленных блока были специализированы, один мог работать со сложными операциями, другой мог обрабатывать две простые операции за раз. В идеальных условиях исполнительные блоки Pentium Pro могли обрабатывать семь микроопераций за такт.

Сегодняшнее OOO ядро также содержит шесть исполнительных блоков. Оно до сих пор содержит блоки загрузки адреса, сохранения адреса и сохранения данных. Однако остальные три немного изменились. Каждый из трех блоков теперь может выполнять простые математические операции или более сложную микрооперацию. Каждый из трех блоков специализирован для конкретных микроопераций, позволяя выполнять работу быстрее, по сравнению с блоками общего назначения. В идеальных условиях нынешнее OOO ядро может обрабатывать 11 микроопераций за такт.

Наконец микрооперация начинает выполняться. Она проходит через более мелкие этапы (отличающиеся между процессорами) и проходит этап отставки. В этот момент микрооперация возвращается во внешний мир и IP начинает указывать на следующую инструкцию. С точки зрения программы, инструкция просто входит в процессор и выходит с другой стороны, точно так же, как это было со старым 8086.

Если вы внимательно читали статью, вы возможно могли заметить очень важную проблему в описании выше. Что произойдет в случае смены места исполнения? Например, что произойдет, если код доходит до if или switch конструкции? В более старых процессорах это значило сброс всей работы в суперскалярном конвейере и ожидание начала обработки новой ветки исполнения.

Ступор конвейера, когда в процессоре находится сотня или более инструкций очень серьезно сказывается на производительности. Каждая инструкция вынуждена ждать, пока инструкции с нового адреса будут загружены и конвейер будет перезапущен. В этой ситуации OOO ядро должно отменить всю текущую работу, откатиться до предыдущего состояния, подождать, пока все микрооперации пройдут отставку, отбросить их вместе с результатами и затем продолжить работу по новому адресу. Эта проблема была очень серьёзной и часто случалась при проектировании. Показатели производительности в такой ситуации были неприемлемы для инженеров. Именно здесь приходит на помощь еще одна важная особенность OOO ядра.

Их ответ был – упреждающее выполнение. Упреждающее выполнение означает, что когда OOO ядро встречает в коде условные конструкции (например if блок), оно просто загрузит и выполнит две ветки кода. Как только ядро понимает, какая ветка верная, результаты второй будут сброшены. Это предотвращает ступор конвейера ценой незначительных издержек на запуск кода в неверной ветке. Также был добавлен кэш для предсказания ветвления (branch prediction cache), который намного улучшил результаты в ситуациях, когда ядро было вынуждено прогнозировать среди множества условных переходов. Ступоры конвейера до сих пор встречаются из-за ветвления, однако это решение позволило сделать их редким исключением, нежели обычным явлением.

Ну и наконец, процессор с HT предоставляет два виртуальных процессора для одного общего OOO ядра. Они разделяют общий ROB и OOO ядро и будут видны для операционной системы как два отдельных процессора. Это выглядит примерно так:

OOO ядро с Hyper-Threading, см. примечание.

Процессор с HT получает два виртуальных процессора, которые взамен поставляют больше данных OOO ядру, что дает увеличение производительности при обычном пользовании. Лишь некоторые тяжелые вычислительные нагрузки, оптимизированные под многопроцессорные системы, могут полностью загрузить OOO ядро. В этом случае HT может несколько понизить производительность. Однако такие нагрузки относительно редки. Для потребителя HT обычно позволяет увеличивать скорость работы примерно вдвое при обычном ежедневном пользовании компьютером.

Пример

Всё это может показаться немного запутанным. Надеюсь, пример расставит всё на свои места.

С точки зрения приложения, мы все ещё работаем на вычислительном конвейере старого 8086. Это чёрный ящик. Инструкция, на которую указывает IP, обрабатывается этим ящиком, и, когда инструкция выходит из него, результаты уже отображены в памяти.

Хотя с точки зрения инструкции, этот чёрный ящик то ещё приключение.

Ниже приводится путь, который совершает инструкция в современном процессоре (2008-2013).

Поехали, вы – инструкция в программе, и эта программа запускается.

Вы терпеливо ждете, пока IP начнет указывать на вас для последующей обработки. Когда IP указывает примерно за 4кб до вашего расположения, или за 1500 инструкций, вы перемещаетесь в кэш инструкций. Загрузка в кэш занимает некоторое время, но это не страшно, так как вы ещё нескоро будете запущены. Эта предзагрузка (prefetch) является частью первого этапа конвейера.

Тем временем IP указывает всё ближе и ближе к вам, и, когда он начинает указывать за 24 инструкции до вас, вы и пять соседних команд отправляетесь в очередь инструкций (instruction queue).

Этот процессор имеет четыре декодера, которые могут вмещать одну сложную команду и до трёх простых. Так случилось, что вы сложная инструкция и были декодированы в четыре микрооперации.

Декодирование – это многоуровневый процесс. Часть декодирования включает в себя анализ на предмет требуемых вами данных и вероятность перехода в какое-то новое место. Декодер зафиксировал потребность в дополнительных данных. Без вашего участия, где-то на другом конце компьютера, нужные вам данные начинают загрузку в кэш данных.

Ваши четыре микрооперации подходят к таблице псевдонимов регистров. Вы объявляете с какого адреса памяти вы читаете (это оказывается fs:[eax+18h]), и чип транслирует его во временный адрес для ваших микроопераций. Ваши микрооперации входят в ROB, откуда, при первой же возможности, двигаются в резервацию.

Резервация содержит инструкции, готовые к исполнению. Ваша третья микрооперация немедленно подхватывается пятым портом исполнения. Вам не известно, почему она была выбрана первой, но её уже нет. Через несколько тактов ваша первая микрооперация устремляется во второй порт, блок загрузки адресов. Оставшиеся микрооперации ждут, пока различные порты подхватывают другие микрооперации. Они ждут, пока второй порт загружает данные из кэша данных во временные слоты памяти.

Долго ждут…

Очень долго ждут…

Другие инструкции приходят и уходят, в то время как ваши микрооперации ждут своего друга, пока тот загружает нужные данные. Хорошо, что этот процессор знает как обрабатывать их внеочерёдно.

Внезапно, обе оставшиеся микрооперации подхватываются нулевым и первым портом, должно быть загрузка данных завершена. Все микрооперации запущены и со временем они вновь встречаются в резервации.

По пути обратно через ворота, микрооперации передают свои билеты с временными адресами. Микрооперации собираются и объединяются, и вы вновь, как инструкция, чувствуете себя единым целым. Процессор вручает вам ваш результат и вежливо направляет к выходу.

Через дверь с пометкой “Отставка” стоит короткая очередь. вы встаете в очередь и обнаруживаете, что вы стоите за той же инструкцией, за которой и заходили. Вы даже стоите в том же порядке. Получается, что OOO ядро действительно знает своё дело.

Со стороны выглядит так, что каждая выходящая из процессора команда выходит по одной, точно в таком же порядке, в каком IP указывал на них.

Заключение

Надеюсь, что эта маленькая лекция пролила немного света на то, что происходит внутри процессора. Как видите, здесь нет магии, дыма и зеркал.

Теперь мы можем ответить на вопросы, заданные в начале статьи.

Так что же происходит внутри процессора? Это сложный мир, где инструкции разбиваются на микрооперации, обрабатываются при первой же возможности и в любом порядке, и вновь собираются воедино, сохраняя свой порядок и расположение. Для внешнего мира выглядит так, будто они обрабатываются последовательно и независимо друг от друга. Но мы теперь знаем, что на самом деле, они обрабатываются внеочерёдно, иногда даже предсказывая и запуская вероятные ветки кода.

Сколько времени уходит на исполнение одной инструкции? Тогда как в бесконвейерном мире для этого имелся хороший ответ, в современном же процессоре всё зависит от того какие инструкции находятся рядом, какой размер соседних кэшей и что в них находится. Есть минимальное время прохождения команды через процессор, но эта величина практически постоянна. Хороший программист или оптимизирующий компилятор может заставить множество инструкций исполняться за среднее время близкое к нулю. Среднее время близкое к нулю – это не время исполнения самой медленной инструкции, а время, требуемое для прохождения инструкции через OOO ядро и время, требуемое кэшу для загрузки и выгрузки данных.

Что значит, когда новый процессор имеет 12, или 18, или даже 31-уровневый конвейер? Это значит, что больше инструкций за раз могут быть приглашены на вечеринку. Очень длинный конвейер может значить, что несколько сотен инструкций могут быть помечены как “обрабатываются” за раз. Когда все идет по плану, OOO ядро постоянно загружено и пропускная способность процессора просто впечатляет. К сожалению, это так же значит, что ступор конвейера перерастает из мелкой неприятности, как это было раньше, в кошмар, так как сотни команд будут вынуждены ожидать очистки конвейера.

Как вы можете применить эти знания в своих программах? Хорошие новости – процессор может предугадать большинство распространённых шаблонов кода, и компиляторы оптимизируют код для OOO ядра уже почти два десятилетия. Процессор лучше всего работает с упорядоченными инструкциями и данными. Всегда пишите простой код. Простой и не извилистый код поможет оптимизатору компилятора найти и ускорить результаты. Если возможно, не создавайте переходы по коду. Если вам необходимо совершать переходы, пытайтесь делать это, следуя определенному шаблону. Сложные дизайны, наподобие динамических таблиц переходов, выглядят классно и многое могут, но ни компилятор, ни процессор, не смогут спрогнозировать какой кусок кода будет выполняться в следующий момент времени. Поэтому сложный код с большой вероятностью будет провоцировать ступоры и неверные предсказания ветвления. Напротив, поддерживайте ваши данные простыми. Организуйте данные упорядоченно, связанно и последовательно для предотвращения ступоров. Правильный выбор структуры и разметки данных может заметно сказаться на повышении производительности. До тех пор, пока ваши данные и код остаются простыми, вы обычно можете положиться на работу оптимизирующего компилятора.

Спасибо, что были частью этого путешествия.

Оригинал — www.gamedev.net/page/resources/_/technical/general-programming/a-journey-through-the-cpu-pipeline-r3115

From Wikipedia, the free encyclopedia

The x86 instruction set refers to the set of instructions that x86-compatible microprocessors support. The instructions are usually part of an executable program, often stored as a computer file and executed on the processor.

The x86 instruction set has been extended several times, introducing wider registers and datatypes as well as new functionality.[1]

x86 integer instructions

[edit]

Below is the full 8086/8088 instruction set of Intel (81 instructions total).[2] These instructions are also available in 32-bit mode, in which they operate on 32-bit registers (eax, ebx, etc.) and values instead of their 16-bit (ax, bx, etc.) counterparts. The updated instruction set is grouped according to architecture (i186, i286, i386, i486, i586/i686) and is referred to as (32-bit) x86 and (64-bit) x86-64 (also known as AMD64).

Original 8086/8088 instructions

[edit]

This is the original instruction set. In the ‘Notes’ column, r means register, m means memory address and imm means immediate (i.e. a value).

Added in specific processors

[edit]

The new instructions added in 80286 add support for x86 protected mode. Some but not all of the instructions are available in real mode as well.

- ^ a b c d The descriptors used by the

LGDT,LIDT,SGDTandSIDTinstructions consist of a 2-part data structure. The first part is a 16-bit value, specifying table size in bytes minus 1. The second part is a 32-bit value (64-bit value in 64-bit mode), specifying the linear start address of the table.

ForLGDTandLIDTwith a 16-bit operand size, the address is ANDed with 00FFFFFFh.On Intel (but not AMD) CPUs, the

SGDTandSIDTinstructions with a 16-bit operand size is – as of Intel SDM revision 079 – documented to write a descriptor to memory with the last byte being set to 0. However, observed behavior is that bits 31:24 of the descriptor table address are written instead.[4] - ^ a b c d The

LGDT,LIDT,LLDTandLTRinstructions are serializing on Pentium and later processors. - ^ The

LMSWinstruction is serializing on Intel processors from Pentium onwards, but not on AMD processors. - ^ On 80386 and later, the «Machine Status Word» is the same as the CR0 control register – however, the

LMSWinstruction can only modify the bottom 4 bits of this register and cannot clear bit 0. The inability to clear bit 0 means thatLMSWcan be used to enter but not leave x86 Protected Mode.

On 80286, it is not possible to leave Protected Mode at all (neither withLMSWnor withLOADALL[5]) without a CPU reset – on 80386 and later, it is possible to leave Protected Mode, but this requires the use of the 80386-and-laterMOVtoCR0instruction. - ^ If

CR4.UMIP=1is set, then theSGDT,SIDT,SLDT,SMSWandSTRinstructions can only run in Ring 0.

These instructions were unprivileged on all x86 CPUs from 80286 onwards until the introduction of UMIP in 2017.[6]

This has been a significant security problem for software-based virtualization, since it enables these instructions to be used by a VM guest to detect that it is running inside a VM.[7] - ^ a b c The

SMSW,SLDTandSTRinstructions always use an operand size of 16 bits when used with a memory argument. With a register argument on 80386 or later processors, wider destination operand sizes are available and behave as follows:SMSW: Stores full CR0 in x86-64 long mode, undefined otherwise.SLDT: Zero-extends 16-bit argument on Pentium Pro and later processors, undefined on earlier processors.STR: Zero-extends 16-bit argument.

- ^ In 64-bit long mode, the

ARPLinstruction is not available – the63 /ropcode has been reassigned to the 64-bit-mode-onlyMOVSXDinstruction. - ^ The

ARPLinstruction causes #UD in Real mode and Virtual 8086 Mode – Windows 95 and OS/2 2.x are known to make extensive use of this #UD to use the63opcode as a one-byte breakpoint to transition from Virtual 8086 Mode to kernel mode.[8][9] - ^ Bits 19:16 of this mask are documented as «undefined» on Intel CPUs.[10] On AMD CPUs, the mask is documented as

0x00FFFF00. - ^ a b For the

LARandLSLinstructions, if the specified segment descriptor could not be loaded, then the instruction’s destination register is left unmodified. - ^ On some Intel CPU/microcode combinations from 2019 onwards, the

VERWinstruction also flushes microarchitectural data buffers. This enables it to be used as part of workarounds for Microarchitectural Data Sampling security vulnerabilities.[11][12] Some of the microarchitectural buffer-flushing functions that have been added toVERWmay require the instruction to be executed with a memory operand.[13] - ^ a b Undocumented, 80286 only.[5][14][15] (A different variant of

LOADALLwith a different opcode and memory layout exists on 80386.)

The 80386 added support for 32-bit operation to the x86 instruction set. This was done by widening the general-purpose registers to 32 bits and introducing the concepts of OperandSize and AddressSize – most instruction forms that would previously take 16-bit data arguments were given the ability to take 32-bit arguments by setting their OperandSize to 32 bits, and instructions that could take 16-bit address arguments were given the ability to take 32-bit address arguments by setting their AddressSize to 32 bits. (Instruction forms that work on 8-bit data continue to be 8-bit regardless of OperandSize. Using a data size of 16 bits will cause only the bottom 16 bits of the 32-bit general-purpose registers to be modified – the top 16 bits are left unchanged.)

The default OperandSize and AddressSize to use for each instruction is given by the D bit of the segment descriptor of the current code segment — D=0 makes both 16-bit, D=1 makes both 32-bit. Additionally, they can be overridden on a per-instruction basis with two new instruction prefixes that were introduced in the 80386:

66h: OperandSize override. Will change OperandSize from 16-bit to 32-bit ifCS.D=0, or from 32-bit to 16-bit ifCS.D=1.67h: AddressSize override. Will change AddressSize from 16-bit to 32-bit ifCS.D=0, or from 32-bit to 16-bit ifCS.D=1.

The 80386 also introduced the two new segment registers FS and GS as well as the x86 control, debug and test registers.

The new instructions introduced in the 80386 can broadly be subdivided into two classes:

- Pre-existing opcodes that needed new mnemonics for their 32-bit OperandSize variants (e.g.

CWDE,LODSD) - New opcodes that introduced new functionality (e.g.

SHLD,SETcc)

For instruction forms where the operand size can be inferred from the instruction’s arguments (e.g. ADD EAX,EBX can be inferred to have a 32-bit OperandSize due to its use of EAX as an argument), new instruction mnemonics are not needed and not provided.

- ^ For the 32-bit string instructions, the ±± notation is used to indicate that the indicated register is post-decremented by 4 if

EFLAGS.DF=1and post-incremented by 4 otherwise.

For the operands where the DS segment is indicated, the DS segment can be overridden by a segment-override prefix – where the ES segment is indicated, the segment is always ES and cannot be overridden.

The choice of whether to use the 16-bit SI/DI registers or the 32-bit ESI/EDI registers as the address registers to use is made by AddressSize, overridable with the67prefix. - ^ The 32-bit string instructions accept repeat-prefixes in the same way as older 8/16-bit string instructions.

ForLODSD,STOSD,MOVSD,INSDandOUTSD, theREPprefix (F3) will repeat the instruction the number of times specified in rCX (CX or ECX, decided by AddressSize), decrementing rCX for each iteration (with rCX=0 resulting in no-op and proceeding to the next instruction).

ForCMPSDandSCASD, theREPE(F3) andREPNE(F2) prefixes are available, which will repeat the instruction, decrementing rCX for each iteration, but only as long as the flag condition (ZF=1 forREPE, ZF=0 forREPNE) holds true AND rCX ≠ 0. - ^ For the

INSB/W/Dinstructions, the memory access rights for theES:[rDI]memory address might not be checked until after the port access has been performed – if this check fails (e.g. page fault or other memory exception), then the data item read from the port is lost. As such, it is not recommended to use this instruction to access an I/O port that performs any kind of side effect upon read. - ^ I/O port access is only allowed when CPL≤IOPL or the I/O port permission bitmap bits for the port to access are all set to 0.

- ^ The

CWDEinstruction differs from the olderCWDinstruction in thatCWDwould sign-extend the 16-bit value in AX into a 32-bit value in the DX:AX register pair. - ^ For the

E3opcode (JCXZ/JECXZ), the choice of whether the instruction will useCXorECXfor its comparison (and consequently which mnemonic to use) is based on the AddressSize, not OperandSize. (OperandSize instead controls whether the jump destination should be truncated to 16 bits or not).

This also applies to the loop instructionsLOOP,LOOPE,LOOPNE(opcodesE0,E1,E2), however, unlikeJCXZ/JECXZ, these instructions have not been given new mnemonics for their ECX-using variants. - ^ For

PUSHA(D), the value of SP/ESP pushed onto the stack is the value it had just before thePUSHA(D)instruction started executing. - ^ For

POPA/POPAD, the stack item corresponding to SP/ESP is popped off the stack (performing a memory read), but not placed into SP/ESP. - ^ The

PUSHFDandPOPFDinstructions will cause a #GP exception if executed in virtual 8086 mode if IOPL is not 3.

ThePUSHF,POPF,IRETandIRETDinstructions will cause a #GP exception if executed in Virtual-8086 mode if IOPL is not 3 and VME is not enabled. - ^ If

IRETDis used to return from kernel mode to user mode (which will entail a CPL change) and the user-mode stack segment indicated by SS is a 16-bit segment, then theIRETDinstruction will only restore the low 16 bits of the stack pointer (ESP/RSP), with the remaining bits keeping whatever value they had in kernel code before theIRETD. This has necessitated complex workarounds on both Linux («ESPFIX»)[16] and Windows.[17] This issue also affects the later 64-bitIRETQinstruction.

- ^ a b c d For the

BT,BTS,BTRandBTCinstructions:- If the first argument to the instruction is a register operand and/or the second argument is an immediate, then the bit-index in the second argument is taken modulo operand size (16/32/64, in effect using only the bottom 4, 5 or 6 bits of the index.)

- If the first argument is a memory operand and the second argument is a register operand, then the bit-index in the second argument is used in full – it is interpreted as a signed bit-index that is used to offset the memory address to use for the bit test.

- ^ a b c The

BTS,BTCandBTRinstructions accept theLOCK(F0) prefix when used with a memory argument – this results in the instruction executing atomically. - ^ If the

F3prefix is used with the0F BC /ropcode, then the instruction will execute asTZCNTon systems that support the BMI1 extension.TZCNTdiffers fromBSFin thatTZCNTbut notBSRis defined to return operand size if the source operand is zero – for other source operand values, they produce the same result (except for flags). - ^ a b

BSFandBSRset the EFLAGS.ZF flag to 1 if the source argument was all-0s and 0 otherwise.

If the source argument was all-0s, then the destination register is documented as being left unchanged on AMD processors, but set to an undefined value on Intel processors. - ^ If the

F3prefix is used with the0F BD /ropcode, then the instruction will execute asLZCNTon systems that support the ABM or LZCNT extensions.LZCNTproduces a different result fromBSRfor most input values. - ^ a b For

SHLDandSHRD, the shift-amount is masked – the bottom 5 bits are used for 16/32-bit operand size and 6 bits for 64-bit operand size.SHLDandSHRDwith 16-bit arguments and a shift-amount greater than 16 produce undefined results. (Actual results differ between different Intel CPUs, with at least three different behaviors known.[18]) - ^ a b The condition codes supported for the

SETccandJcc nearinstructions (opcodes0F 9x /0and0F 8xrespectively, with the x nibble specifying the condition) are:

x cc Condition (EFLAGS) 0 O OF=1: «Overflow» 1 NO OF=0: «Not Overflow» 2 C,B,NAE CF=1: «Carry», «Below», «Not Above or Equal» 3 NC,NB,AE CF=0: «Not Carry», «Not Below», «Above or Equal» 4 Z,E ZF=1: «Zero», «Equal» 5 NZ,NE ZF=0: «Not Zero», «Not Equal» 6 NA,BE (CF=1 or ZF=1): «Not Above», «Below or Equal» 7 A,NBE (CF=0 and ZF=0): «Above», «Not Below or Equal» 8 S SF=1: «Sign» 9 NS SF=0: «Not Sign» A P,PE PF=1: «Parity», «Parity Even» B NP,PO PF=0: «Not Parity», «Parity Odd» C L,NGE SF≠OF: «Less», «Not Greater Or Equal» D NL,GE SF=OF: «Not Less», «Greater Or Equal» E LE,NG (ZF=1 or SF≠OF): «Less or Equal», «Not Greater» F NLE,G (ZF=0 and SF=OF): «Not Less or Equal», «Greater» - ^ For

SETcc, while the opcode is commonly specified as /0 – implying that bits 5:3 of the instruction’s ModR/M byte should be 000 – modern x86 processors (Pentium and later) ignore bits 5:3 and will execute the instruction asSETccregardless of the contents of these bits. - ^ For

LFS,LGSandLSS, the size of the offset part of the far pointer is given by operand size – the size of the segment part is always 16 bits. In 64-bit mode, using theREX.Wprefix with these instructions will cause them to load a far pointer with a 64-bit offset on Intel but not AMD processors. - ^ a b c d e f For

MOVto/from theCRx,DRxandTRxregisters, the reg part of the ModR/M byte is used to indicateCRx/DRx/TRxregister and r/m part the general-register.Uniquely for the

MOV CRx/DRx/TRxopcodes, the top two bits of the ModR/M byte is ignored – these opcodes are decoded and executed as if the top two bits of the ModR/M byte are11b. - ^ a b c d For moves to/from the

CRxandDRxregisters, the operand size is always 64 bits in 64-bit mode and 32 bits otherwise. - ^ On processors that support global pages (Pentium and later), global page table entries will not be flushed by a

MOVtoCR3− instead, these entries can be flushed by toggling the CR4.PGE bit.

On processors that support PCIDs, writing to CR3 while PCIDs are enabled will only flush TLB entries belonging to the PCID specified in bits 11:0 of the value written to CR3 (this flush can be suppressed by setting bit 63 of the written value to 1). Flushing pages belonging to other PCIDs can instead be done by toggling the CR4.PGE bit, clearing the CR4.PCIDE bit, or using theINVPCIDinstruction. - ^ On processors prior to Pentium, moves to

CR0would not serialize the instruction stream – in part for this reason, it is usually required to perform a far jump[19] immediately after aMOVtoCR0if such aMOVis used to enable/disable protected mode and/or memory paging.MOVtoCR2is architecturally listed as serializing, but has been reported to be non-serializing on at least some Intel Core-i7 processors.[20]MOVtoCR8(introduced with x86-64) is serializing on AMD but not Intel processors. - ^ a b The

MOV TRxinstructions were discontinued from Pentium onwards. - ^ The

INT1/ICEBP(F1) instruction is present on all known Intel x86 processors from the 80386 onwards,[21] but only fully documented for Intel processors from the May 2018 release of the Intel SDM (rev 067) onwards.[22] Before this release, mention of the instruction in Intel material was sporadic, e.g. AP-526 rev 001.[23]

For AMD processors, the instruction has been documented since 2002.[24] - ^ The operation of the

F1(ICEBP) opcode differs from the operation of the regular software interrupt opcodeCD 01in several ways:- In protected mode,

- In virtual-8086 mode,

CD 01will also check CPL against IOPL as an access-rights check, whileF1will not. - In virtual-8086 mode with VME enabled, interrupt redirection is supported for

CD 01but notF1.

CD 01will check CPL against the interrupt descriptor’s DPL field as an access-rights check, whileF1will not. - In virtual-8086 mode,

- ^ The UMOV instruction is present on 386 and 486 processors only.[21]

- ^ a b The

XBTSandIBTSinstructions were discontinued with the B1 stepping of 80386.

They have been used by software mainly for detection of the buggy[25] B0 stepping of the 80386. Microsoft Windows (v2.01 and later) will attempt to run theXBTSinstruction as part of its CPU detection ifCPUIDis not present, and will refuse to boot ifXBTSis found to be working.[26] - ^ a b For

XBTSandIBTS, the r/m argument represents the data to extract/insert a bitfield from/to, the reg argument the bitfield to be inserted/extracted, AX/EAX a bit-offset and CL a bitfield length.[27] - ^ Undocumented, 80386 only.[28]

| Instruction | Opcode | Description | Ring |

|---|---|---|---|

BSWAP r32

|

0F C8+r

|

Byte Order Swap. Usually used to convert between big-endian and little-endian data representations. For 32-bit registers, the operation performed is:

r = (r << 24)

| ((r << 8) & 0x00FF0000)

| ((r >> 8) & 0x0000FF00)

| (r >> 24);

Using |

3 |

CMPXCHG r/m8,r8

|

0F B0 /r[b]

|

Compare and Exchange. If accumulator (AL/AX/EAX/RAX) compares equal to first operand,[c] then EFLAGS.ZF is set to 1 and the first operand is overwritten with the second operand. Otherwise, EFLAGS.ZF is set to 0, and first operand is copied into the accumulator.

Instruction atomic only if used with |

|

CMPXCHG r/m,r16CMPXCHG r/m,r32

|

0F B1 /r[b]

|

||

XADD r/m,r8

|

0F C0 /r

|

eXchange and ADD. Exchanges the first operand with the second operand, then stores the sum of the two values into the destination operand.

Instruction atomic only if used with |

|

XADD r/m,r16XADD r/m,r32

|

0F C1 /r

|

||

INVLPG m8

|

0F 01 /7

|

Invalidate the TLB entries that would be used for the 1-byte memory operand.[d]

Instruction is serializing. |

0 |

INVD

|

0F 08

|

Invalidate Internal Caches.[e] Modified data in the cache are not written back to memory, potentially causing data loss.[f] | |

WBINVD

|

NFx 0F 09[g]

|

Write Back and Invalidate Cache.[e] Writes back all modified cache lines in the processor’s internal cache to main memory and invalidates the internal caches. |

- ^ Using

BSWAPwith 16-bit registers is not disallowed per se (it will execute without producing an #UD or other exceptions) but is documented to produce undefined results – it is reported to produce various different results on 486,[29] 586, and Bochs/QEMU.[30] - ^ a b On Intel 80486 stepping A,[31] the

CMPXCHGinstruction uses a different encoding —0F A6 /rfor 8-bit variant,0F A7 /rfor 16/32-bit variant. The0F B0/B1encodings are used on 80486 stepping B and later.[32][33] - ^ The

CMPXCHGinstruction setsEFLAGSin the same way as aCMPinstruction that uses the accumulator (AL/AX/EAX/RAX) as its first argument would do. - ^

INVLPGexecutes as no-operation if the m8 argument is invalid (e.g. unmapped page or non-canonical address).INVLPGcan be used to invalidate TLB entries for individual global pages. - ^ a b The

INVDandWBINVDinstructions will invalidate all cache lines in the CPU’s L1 caches. It is implementation-defined whether they will invalidate L2/L3 caches as well.

These instructions are serializing – on some processors, they may block interrupts until completion as well. - ^ Under Intel VT-x virtualization, the

INVDinstruction will cause a mandatory #VMEXIT. Also, on processors that support Intel SGX, if the PRM (Processor Reserved Memory) has been set up by using the PRMRRs (PRM range registers), then theINVDinstruction is not permitted and will cause a #GP(0) exception.[34] - ^ If the

F3prefix is used with the0F 09opcode, then the instruction will execute asWBNOINVDon processors that support the WBNOINVD extension – this will not invalidate the cache.

Integer/system instructions that were not present in the basic 80486 instruction set, but were added in various x86 processors prior to the introduction of SSE. (Discontinued instructions are not included.)

- ^ a b c In 64-bit mode, the

RDMSR,RDTSCandRDPMCinstructions will set the top 32 bits of RDX and RAX to zero. - ^ On Intel and AMD CPUs, the

WRMSRinstruction is also used to update the CPU microcode. This is done by writing the virtual address of the new microcode to upload to MSR79hon Intel CPUs and MSRC001_0020h[36] on AMD CPUs. - ^ Writes to the following MSRs are not serializing:[37][38]

Number Name 48hSPEC_CTRL 49hPRED_CMD 10BhFLUSH_CMD 122hTSX_CTRL 6E0hTSC_DEADLINE 6E1hPKRS 774hHWP_REQUEST

(non-serializing only if the FAST_IA32_HWP_REQUEST bit it set)802hto83Fh(x2APIC MSRs) 1B01hUARCH_MISC_CTL C001_0100hFS_BASE (non-serializing on AMD Zen 4 and later)[39] C001_0101hGS_BASE (Zen 4 and later) C001_0102hKernelGSbase (Zen 4 and later) C001_011BhDoorbell Register (AMD-specific) WRMSRto the x2APIC ICR (Interrupt Command Register; MSR830h) is commonly used to produce an IPI (Inter-processor interrupt) — on Intel[40] but not AMD[41] CPUs, such an IPI can be reordered before an older memory store. - ^ System Management Mode and the

RSMinstruction were made available on non-SL variants of the Intel 486 only after the initial release of the Intel Pentium in 1993. - ^ On some older 32-bit processors, executing

CPUIDwith a leaf index (EAX) greater than 0 may leave EBX and ECX unmodified, keeping their old values. For this reason, it is recommended to zero out EBX and ECX before executingCPUID.

Processors noted to exhibit this behavior include Cyrix MII[46] and IDT WinChip 2.[47]In 64-bit mode,

CPUIDwill set the top 32 bits of RAX, RBX, RCX and RDX to zero. - ^ On some Intel processors starting from Ivy Bridge, there exists MSRs that can be used to restrict

CPUIDto ring 0. Such MSRs are documented for at least Ivy Bridge[48] and Denverton.[49]

The ability to restrictCPUIDto ring 0 also exists on AMD processors supporting the «CpuidUserDis» feature (Zen 4 «Raphael» and later).[50] - ^ a b

CPUIDis also available on some Intel and AMD 486 processor variants that were released after the initial release of the Intel Pentium. - ^ On the Cyrix 5×86 and 6×86 CPUs,

CPUIDis not enabled by default and must be enabled through a Cyrix configuration register. - ^ On NexGen CPUs,

CPUIDis only supported with some system BIOSes. On some NexGen CPUs that do supportCPUID, EFLAGS.ID is not supported but EFLAGS.AC is, complicating CPU detection.[51] - ^ Unlike the older

CMPXCHGinstruction, theCMPXCHG8Binstruction does not modify any EFLAGS bits other than ZF. - ^

LOCK CMPXCHG8Bwith a register operand (which is an invalid encoding) will, on some Intel Pentium CPUs, cause a hang rather than the expected #UD exception — this is known as the Pentium F00F bug. - ^ a b c On IDT WinChip, Transmeta Crusoe and Rise mP6 processors, the

CMPXCHG8Binstruction is always supported, however its CPUID bit may be missing. This is a workaround for a bug in Windows NT.[52] - ^ a b The

RDTSCandRDPMCinstructions are not ordered with respect to other instructions, and may sample their respective counters before earlier instructions are executed or after later instructions have executed. Invocations ofRDPMC(but notRDTSC) may be reordered relative to each other even for reads of the same counter.

In order to impose ordering with respect to other instructions,LFENCEor serializing instructions (e.g.CPUID) are needed.[53] - ^ Fixed-rate TSC was introduced in two stages:

- Constant TSC

- TSC running at a fixed rate as long as the processor core is not in a deep-sleep (C2 or deeper) mode, but not synchronized between CPU cores. Introduced in Intel Prescott, Yonah and Bonnell. Also present in all Transmeta and VIA Nano[54] CPUs. Does not have a CPUID bit.

- Invariant TSC

- TSC running at a fixed rate, and remaining synchronized between CPU cores in all P-,C- and T-states (but not necessarily S-states).

Present in AMD K10 and later; Intel Nehalem/Saltwell[55] and later; Zhaoxin WuDaoKou[56] and later. Indicated with a CPUID bit (leaf8000_0007:EDX[8]).

- ^

RDTSCcan be run outside Ring 0 only ifCR4.TSD=0.

On Intel Pentium and AMD K5,RDTSCcannot be run in Virtual-8086 mode.[57] Later processors removed this restriction. - ^

RDPMCcan be run outside Ring 0 only ifCR4.PCE=1. - ^ The

RDPMCinstruction is not present in VIA processors prior to the Nano. - ^ The condition codes supported for

CMOVccinstruction (opcode0F 4x /r, with the x nibble specifying the condition) are:

x cc Condition (EFLAGS) 0 O OF=1: «Overflow» 1 NO OF=0: «Not Overflow» 2 C,B,NAE CF=1: «Carry», «Below», «Not Above or Equal» 3 NC,NB,AE CF=0: «Not Carry», «Not Below», «Above or Equal» 4 Z,E ZF=1: «Zero», «Equal» 5 NZ,NE ZF=0: «Not Zero», «Not Equal» 6 NA,BE (CF=1 or ZF=1): «Not Above», «Below or Equal» 7 A,NBE (CF=0 and ZF=0): «Above», «Not Below or Equal» 8 S SF=1: «Sign» 9 NS SF=0: «Not Sign» A P,PE PF=1: «Parity», «Parity Even» B NP,PO PF=0: «Not Parity», «Parity Odd» C L,NGE SF≠OF: «Less», «Not Greater Or Equal» D NL,GE SF=OF: «Not Less», «Greater Or Equal» E LE,NG (ZF=1 or SF≠OF): «Less or Equal», «Not Greater» F NLE,G (ZF=0 and SF=OF): «Not Less or Equal», «Greater» - ^ In 64-bit mode,

CMOVccwith a 32-bit operand size will clear the upper 32 bits of the destination register even if the condition is false.

ForCMOVccwith a memory source operand, the CPU will always read the operand from memory – potentially causing memory exceptions and cache line-fills – even if the condition for the move is not satisfied. (The Intel APX extension defines a set of new EVEX-encoded variants ofCMOVccthat will suppress memory exceptions if the condition is false.) - ^ On pre-Nehemiah VIA C3 variants («Samuel»/»Ezra»), the

reg,regbut notreg,[mem]forms of theCMOVccinstructions have been reported to be present as undocumented instructions.[58] - ^ Intel’s recommended byte encodings for multi-byte NOPs of lengths 2 to 9 bytes in 32/64-bit mode are (in hex):[59]

Length Byte Sequence 2 66 903 0F 1F 004 0F 1F 40 005 0F 1F 44 00 006 66 0F 1F 44 00 007 0F 1F 80 00 00 00 008 0F 1F 84 00 00 00 00 009 66 0F 1F 84 00 00 00 00 00For cases where there is a need to use more than 9 bytes of NOP padding, it is recommended to use multiple NOPs.

- ^ Unlike other instructions added in Pentium Pro, long NOP does not have a CPUID feature bit.

- ^

0F 1F /0as long-NOP was introduced in the Pentium Pro, but remained undocumented until 2006.[61]

The whole0F 18..1Fopcode range wasNOPin Pentium Pro. However, except for0F 1F /0, Intel does not guarantee that these opcodes will remainNOPin future processors, and have indeed assigned some of these opcodes to other instructions in at least some processors.[62] - ^ Documented for AMD x86-64 since 2002.[63]

- ^ While the

0F 0Bopcode was officially reserved as an invalid opcode from Pentium onwards, it only got assigned the mnemonicUD2from Pentium Pro onwards.[65] - ^ a b GNU Binutils have used the

UD2AandUD2Bmnemonics for the0F 0Band0F B9opcodes since version 2.7.[66]

NeitherUD2AnorUD2Boriginally took any arguments —UD2Bwas later modified to accept a ModR/M byte, in Binutils version 2.30.[67] - ^ The

UD2(0F 0B) instruction will additionally stop subsequent bytes from being decoded as instructions, even speculatively. For this reason, if an indirect branch instruction is followed by something that is not code, it is recommended to place anUD2instruction after the indirect branch.[68] - ^ a b The UD0/1/2 opcodes —

0F 0B,0F B9and0F FF— will cause an #UD exception on all x86 processors from the 80186 onwards (except NEC V-series processors), but did not get explicitly reserved for this purpose until P5-class processors. - ^ While the

0F B9opcode was officially reserved as an invalid opcode from Pentium onwards, it only got assigned its mnemonicUD1much later – AMD APM started listingUD1in its opcode maps from rev 3.17 onwards,[70] while Intel SDM started listing it from rev 061 onwards.[71] - ^ a b For both the

0F B9and0F FFopcodes, different x86 implementations are known to differ regarding whether the opcodes accept a ModR/M byte.[72][73][74] - ^ For the

0F FFopcode, theOIOmnemonic was introduced by Cyrix,[75] while theUD0menmonic (without arguments) was introduced by AMD and Intel at the same time as theUD1mnemonic for0F B9.[70][71] Later Intel (but not AMD) documentation modified its description ofUD0to add a ModR/M byte and take two arguments.[76] - ^ On K6, the

SYSCALL/SYSRETinstructions were available on Model 7 (250nm «Little Foot») and later, not on the earlier Model 6.[78] - ^

SYSCALLandSYSRETwere made an integral part of x86-64 – as a result, the instructions are available in 64-bit mode on all x86-64 processors from AMD, Intel, VIA and Zhaoxin.

Outside 64-bit mode, the instructions are available on AMD processors only. - ^ The exact semantics of

SYSRETdiffers slightly between AMD and Intel processors: non-canonical return addresses cause a #GP exception to be thrown in Ring 3 on AMD CPUs but Ring 0 on Intel CPUs. This has been known to cause security issues.[79] - ^ a b For the

SYSRETandSYSEXITinstructions under x86-64, it is necessary to add theREX.Wprefix for variants that will return to 64-bit user-mode code.

Encodings of these instructions without theREX.Wprefix are used to return to 32-bit user-mode code. (Neither of these instructions can be used to return to 16-bit user-mode code — for return to 16-bit code,IRET/IRETD/IRETQshould be used.) - ^ a b c The

SYSRET,SYSENTERandSYSEXITinstructions are unavailable in Real mode. (SYSENTERis, however, available in Virtual 8086 mode.) - ^ The

CPUIDflags that indicate support forSYSENTER/SYSEXITare set on the Pentium Pro, even though the processor does not officially support these instructions.[80]

Third party testing indicates that the opcodes are present on the Pentium Pro but too buggy to be usable.[81] - ^ On AMD CPUs, the

SYSENTERandSYSEXITinstructions are not available in x86-64 long mode (#UD). - ^ On Transmeta CPUs, the

SYSENTERandSYSEXITinstructions are only available with version 4.2 or higher of the Transmeta Code Morphing software.[83] - ^ On Nehemiah,

SYSENTERandSYSEXITare available only on stepping 8 and later.[84]

Added as instruction set extensions

[edit]

These instructions can only be encoded in 64 bit mode. They fall in four groups:

- original instructions that reuse existing opcodes for a different purpose (

MOVSXDreplacingARPL) - original instructions with new opcodes (

SWAPGS) - existing instructions extended to a 64 bit address size (

JRCXZ) - existing instructions extended to a 64 bit operand size (remaining instructions)

Most instructions with a 64 bit operand size encode this using a REX.W prefix; in the absence of the REX.W prefix,

the corresponding instruction with 32 bit operand size is encoded. This mechanism also applies to most other instructions with 32 bit operand

size. These are not listed here as they do not gain a new mnemonic in Intel syntax when used with a 64 bit operand size.

| Instruction | Encoding | Meaning | Ring |

|---|---|---|---|

CDQE

|

REX.W 98

|

Sign extend EAX into RAX | 3 |

CQO

|

REX.W 99

|

Sign extend RAX into RDX:RAX | |

CMPSQ

|

REX.W A7

|

CoMPare String Quadword | |

CMPXCHG16B m128[a][b]

|

REX.W 0F C7 /1

|

CoMPare and eXCHanGe 16 Bytes. Atomic only if used with LOCK prefix. |

|

IRETQ

|

REX.W CF

|

64-bit Return from Interrupt | |

JRCXZ rel8

|

E3 cb

|

Jump if RCX is zero | |

LODSQ

|

REX.W AD

|

LoaD String Quadword | |

MOVSXD r64,r/m32

|

REX.W 63 /r[c]

|

MOV with Sign Extend 32-bit to 64-bit | |

MOVSQ

|

REX.W A5

|

Move String Quadword | |

POPFQ

|

9D

|

POP RFLAGS Register | |

PUSHFQ

|

9C

|

PUSH RFLAGS Register | |

SCASQ

|

REX.W AF

|

SCAn String Quadword | |

STOSQ

|

REX.W AB

|

STOre String Quadword | |

SWAPGS

|

0F 01 F8

|

Exchange GS base with KernelGSBase MSR | 0 |

- ^ The memory operand to

CMPXCHG16Bmust be 16-byte aligned. - ^ The

CMPXCHG16Binstruction was absent from a few of the earliest Intel/AMD x86-64 processors. On Intel processors, the instruction was missing from Xeon «Nocona» stepping D,[85] but added in stepping E.[86] On AMD K8 family processors, it was added in stepping F, at the same time as DDR2 support was introduced.[87]

For this reason,CMPXCHG16Bhas its own CPUID flag, separate from the rest of x86-64. - ^ Encodings of

MOVSXDwithout REX.W prefix are permitted but discouraged[88] – such encodings behave identically to 16/32-bitMOV(8B /r).

Bit manipulation extensions

[edit]

Bit manipulation instructions. For all of the VEX-encoded instructions defined by BMI1 and BMI2, the operand size may be 32 or 64 bits, controlled by the VEX.W bit – none of these instructions are available in 16-bit variants. The VEX-encoded instructions are not available in Real Mode and Virtual-8086 mode — other than that, the bit manipulation instructions are available in all operating modes on supported CPUs.

| Bit Manipulation Extension | Instruction mnemonics |

Opcode | Instruction description | Added in |

|---|---|---|---|---|

|

POPCNT r16,r/m16POPCNT r32,r/m32

|

F3 0F B8 /r

|

Population Count. Counts the number of bits that are set to 1 in its source argument. | K10, Bobcat, Haswell, ZhangJiang, Gracemont |

POPCNT r64,r/m64

|

F3 REX.W 0F B8 /r

|

|||

LZCNT r16,r/m16LZCNT r32,r/m32

|

F3 0F BD /r

|

Count Leading zeroes.[b] If source operand is all-0s, then LZCNT will return operand size in bits (16/32/64) and set CF=1.

|

||

LZCNT r64,r/m64

|

F3 REX.W 0F BD /r

|

|||

|

TZCNT r16,r/m16TZCNT r32,r/m32

|

F3 0F BC /r

|

Count Trailing zeroes.[c] If source operand is all-0s, then TZCNT will return operand size in bits (16/32/64) and set CF=1.

|

Haswell, Piledriver, Jaguar, ZhangJiang, Gracemont |

TZCNT r64,r/m64

|

F3 REX.W 0F BC /r

|

|||

ANDN ra,rb,r/m

|

VEX.LZ.0F38 F2 /r

|

Bitwise AND-NOT: ra = r/m AND NOT(rb)

|

||

BEXTR ra,r/m,rb

|

VEX.LZ.0F38 F7 /r

|

Bitfield extract. Bitfield start position is specified in bits [7:0] of rb, length in bits[15:8] of rb. The bitfield is then extracted from the r/m value with zero-extension, then stored in ra. Equivalent to[d]

mask = (1 << rb[15:8]) - 1 ra = (r/m >> rb[7:0]) AND mask |

||

BLSI reg,r/m

|

VEX.LZ.0F38 F3 /3

|

Extract lowest set bit in source argument. Returns 0 if source argument is 0. Equivalent todst = (-src) AND src

|

||

BLSMSK reg,r/m

|

VEX.LZ.0F38 F3 /2

|

Generate a bitmask of all-1s bits up to the lowest bit position with a 1 in the source argument. Returns all-1s if source argument is 0. Equivalent to dst = (src-1) XOR src

|

||

BLSR reg,r/m

|

VEX.LZ.0F38 F3 /1

|

Copy all bits of the source argument, then clear the lowest set bit. Equivalent todst = (src-1) AND src

|

||

|

BZHI ra,r/m,rb

|

VEX.LZ.0F38 F5 /r

|

Zero out high-order bits in r/m starting from the bit position specified in rb, then write result to rd. Equivalent tora = r/m AND NOT(-1 << rb[7:0])

|

Haswell, Excavator,[e] ZhangJiang, Gracemont |

MULX ra,rb,r/m

|

VEX.LZ.F2.0F38 F6 /r

|

Widening unsigned integer multiply without setting flags. Multiplies EDX/RDX with r/m, then stores the low half of the multiplication result in ra and the high half in rb. If ra and rb specify the same register, only the high half of the result is stored.

|

||

PDEP ra,rb,r/m

|

VEX.LZ.F2.0F38 F5 /r

|

Parallel Bit Deposit. Scatters contiguous bits from rb to the bit positions set in r/m, then stores result to ra. Operation performed is:

ra=0; k=0; mask=r/m

for i=0 to opsize-1 do

if (mask[i] == 1) then

ra[i]=rb[k]; k=k+1

|

||

PEXT ra,rb,r/m

|

VEX.LZ.F3.0F38 F5 /r

|

Parallel Bit Extract. Uses r/m argument as a bit mask to select bits in rb, then compacts the selected bits into a contiguous bit-vector. Operation performed is:

ra=0; k=0; mask=r/m

for i=0 to opsize-1 do

if (mask[i] == 1) then

ra[k]=rb[i]; k=k+1

|

||

RORX reg,r/m,imm8

|

VEX.LZ.F2.0F3A F0 /r ib

|

Rotate right by immediate without affecting flags. | ||

SARX ra,r/m,rb

|

VEX.LZ.F3.0F38 F7 /r

|

Arithmetic shift right without updating flags. For SARX, SHRX and SHLX, the shift-amount specified in rb is masked to 5 bits for 32-bit operand size and 6 bits for 64-bit operand size.

|

||

SHRX ra,r/m,rb

|

VEX.LZ.F2.0F38 F7 /r

|

Logical shift right without updating flags. | ||

SHLX ra,r/m,rb

|

VEX.LZ.66.0F38 F7 /r

|

Shift left without updating flags. |

- ^ On AMD CPUs, the «ABM» extension provides both

POPCNTandLZCNT. On Intel CPUs, however, the CPUID bit for «ABM» is only documented to indicate the presence of theLZCNTinstruction and is listed as «LZCNT», whilePOPCNThas its own separate CPUID feature bit.

However, all known processors that implement the «ABM»/»LZCNT» extensions also implementPOPCNTand set the CPUID feature bit for POPCNT, so the distinction is theoretical only.

(The converse is not true – there exist processors that supportPOPCNTbut not ABM, such as Intel Nehalem and VIA Nano 3000.) - ^ The

LZCNTinstruction will execute asBSRon systems that do not support the LZCNT or ABM extensions.BSRcomputes the index of the highest set bit in the source operand, producing a different result fromLZCNTfor most input values. - ^ The

TZCNTinstruction will execute asBSFon systems that do not support the BMI1 extension.BSFproduces the same result asTZCNTfor all input operand values except zero – for whichTZCNTreturns input operand size, butBSFproduces undefined behavior (leaves destination unmodified on most modern CPUs). - ^ For

BEXTR, the start position and length are not masked and can take values from 0 to 255. If the selected bits extend beyond the end of ther/margument (which has the usual 32/64-bit operand size), then the out-of-bounds bits are read out as 0. - ^ On AMD processors before Zen 3, the

PEXTandPDEPinstructions are quite slow[89] and exhibit data-dependent timing due to the use of a microcoded implementation (about 18 to 300 cycles, depending on the number of bits set in the mask argument). As a result, it is often faster to use other instruction sequences on these processors.[90][91]

Added with Intel TSX

[edit]

| TSX Subset | Instruction | Opcode | Description | Added in |

|---|---|---|---|---|

|

XBEGIN rel16XBEGIN rel32

|

C7 F8 cwC7 F8 cd

|

Start transaction. If transaction fails, perform a branch to the given relative offset. | Haswell (Deprecated on desktop/laptop CPUs from 10th generation (Ice Lake, Comet Lake) onwards, but continues to be available on Xeon-branded server parts (e.g. Ice Lake-SP, Sapphire Rapids)) |

XABORT imm8

|

C6 F8 ib

|

Abort transaction with 8-bit immediate as error code. | ||

XEND

|

NP 0F 01 D5

|

End transaction. | ||

XTEST

|

NP 0F 01 D6

|

Test if in transactional execution. Sets EFLAGS.ZF to 0 if executed inside a transaction (RTM or HLE), 1 otherwise.

|

||

|

XACQUIRE

|

F2

|

Instruction prefix to indicate start of hardware lock elision, used with memory atomic instructions only (for other instructions, the F2 prefix may have other meanings). When used with such instructions, may start a transaction instead of performing the memory atomic operation.

|

Haswell (Discontinued – the last processors to support HLE were Coffee Lake and Cascade Lake) |

XRELEASE

|

F3

|

Instruction prefix to indicate end of hardware lock elision, used with memory atomic/store instructions only (for other instructions, the F3 prefix may have other meanings). When used with such instructions during hardware lock elision, will end the associated transaction instead of performing the store/atomic.

|

||

|

XSUSLDTRK

|

F2 0F 01 E8

|

Suspend Tracking Load Addresses | Sapphire Rapids |

XRESLDTRK

|

F2 0F 01 E9

|

Resume Tracking Load Addresses |

Intel CET (Control-Flow Enforcement Technology) adds two distinct features to help protect against security exploits such as return-oriented programming: a shadow stack (CET_SS), and indirect branch tracking (CET_IBT).

| CET Subset | Instruction | Opcode | Description | Ring | Added in |

|---|---|---|---|---|---|

|

INCSSPD r32

|

F3 0F AE /5

|

Increment shadow stack pointer | 3 | Tiger Lake, Zen 3 |

INCSSPQ r64

|

F3 REX.W 0F AE /5

|

||||

RDSSPD r32

|

F3 0F 1E /1

|

Read shadow stack pointer into register (low 32 bits)[a] | |||

RDSSPQ r64

|

F3 REX.W 0F 1E /1

|

Read shadow stack pointer into register (full 64 bits)[a] | |||

SAVEPREVSSP

|

F3 0F 01 EA

|

Save previous shadow stack pointer | |||

RSTORSSP m64

|

F3 0F 01 /5

|

Restore saved shadow stack pointer | |||

WRSSD m32,r32

|

NP 0F 38 F6 /r

|

Write 4 bytes to shadow stack | |||

WRSSQ m64,r64

|

NP REX.W 0F 38 F6 /r

|

Write 8 bytes to shadow stack | |||

WRUSSD m32,r32

|

66 0F 38 F5 /r

|

Write 4 bytes to user shadow stack | 0 | ||

WRUSSQ m64,r64

|

66 REX.W 0F 38 F5 /r

|

Write 8 bytes to user shadow stack | |||

SETSSBSY

|

F3 0F 01 E8

|

Mark shadow stack busy | |||

CLRSSBSY m64

|

F3 0F AE /6

|

Clear shadow stack busy flag | |||

|

ENDBR32

|

F3 0F 1E FB

|

Terminate indirect branch in 32-bit mode[b] | 3 | Tiger Lake |

ENDBR64

|

F3 0F 1E FA

|

Terminate indirect branch in 64-bit mode[b] | |||

NOTRACK

|

3E[c]

|

Prefix used with indirect CALL/JMP near instructions (opcodes FF /2 and FF /4) to indicate that the branch target is not required to start with an ENDBR32/64 instruction. Prefix only honored when NO_TRACK_EN flag is set.

|

- ^ a b The

RDSSPDandRDSSPQinstructions act as NOPs on processors where shadow stacks are disabled or CET is not supported. - ^ a b